**Universidade de Brasília

Faculdade de Tecnologia

Departamento de Engenharia Mecânica**

**Desenvolvimento e implementação de blocos

digitais para um transceptor UWB baseado em

um RISC-V**

Hércules Ismael de Abreu Santos

**DISSERTAÇÃO DE MESTRADO

PROGRAMA DE PÓS-GRADUAÇÃO EM SISTEMAS MECATRÔNICOS**

Brasília

2025

**Universidade de Brasília

Faculdade de Tecnologia

Departamento de Engenharia Mecânica**

**Desenvolvimento e implementação de blocos

digitais para um transceptor UWB baseado em

um RISC-V**

Hércules Ismael de Abreu Santos

Dissertação de Mestrado submetida ao Departamento de Engenharia Mecânica da Universidade Brasília como parte dos requisitos necessários para a obtenção do grau de Mestre

Orientador: Prof. Dr. Jones Yudi Mori Alves da Silva

Coorientador: Prof. Dr. Gilmar Silva Beserra

Brasília

2025

S769 Santos, Hércules Ismael de Abreu.

Desenvolvimento e implementação de blocos digitais para

um transceptor UWB baseado em um RISC-V / Hércules Ismael

de Abreu Santos; orientador Jones Yudi Mori Alves da Silva; co-

orientador Gilmar Silva Beserra. -- Brasília, 2025.

80 p.

Dissertação de Mestrado (Programa de Pós-Graduação em

Sistemas Mecatrônicos) -- Universidade de Brasília, 2025.

1. RISC-V. 2. IEEE 802.15.6. 3. IoT. I. Silva, Jones Yudi Mori

Alves da, orient. II. Beserra, Gilmar Silva, coorient. III. Título

**Universidade de Brasília

Faculdade de Tecnologia

Departamento de Engenharia Mecânica**

**Desenvolvimento e implementação de blocos digitais

para um transceptor UWB baseado em um RISC-V**

Hércules Ismael de Abreu Santos

Dissertação de Mestrado submetida ao Departamento de Engenharia Mecânica da Universidade Brasília como parte dos requisitos necessários para a obtenção do grau de Mestre

Trabalho aprovado. Brasília, 28 de março de 2025:

---

**Prof. Dr. Jones Yudi Mori Alves da Silva,

UnB/FT/ENM**

Orientador

---

**Prof. Dr. Gilmar Silva Beserra, UnB/FCTE**

Co-Orientador

---

**Prof. Dr. Leonardo Londero de Oliveira,

UFSM/DELC**

Examinador externo

---

**Prof. Dr. Wellington Avelino do Amaral,

UnB/FCTE**

Examinador interno

Brasília

2025

# Agradecimentos

Quero agradecer primeiramente a minha família por me dar suporte no decorrer do curso. Agradeço a meu pai, que já não está entre os vivos, mas representa para mim o maior exemplo de homem que tive, e agradeço a minha mãe por me dar suporte e estar comigo. Agradeço também as meus tios José Martins e Creuza Abreu por participarem de uma parte importante da minha criação.

Agradeço a meus professores pelas aulas instrutivas e agradeço também ao meu orientador Jones Yudi e meu coorientador Gilmar Beserra, por me orientarem, tirando dúvidas e fornecendo direções para realizar este trabalho.

*“All models are wrong, but some are useful.”*

*(George Box)*

# Resumo

Sistemas IoT atuais requerem a integração de diversas funcionalidades como leitura de sensores, comunicação sem fio, processamento de dados e demandam realizar estas funções em baixo consumo de energia. Uma tecnologia promissora de comunicação sem fio que pode ser utilizada em aplicações IoT de baixa potência é o UWB, que permite a transmissão de dados em uma velocidade considerável com um consumo baixo de energia. Para implementar esta tecnologia, uma boa prática é seguir o padrão IEEE 802.15.6 para redes WBAN, que padroniza a implementação de sistemas UWB. Este trabalho tem o objetivo de implementar um sistema DSP para controlar um SoC que transmite dados via UWB. Para isto foi implementado a parte digital da camada física do UWB, prevista na norma IEEE 802.15.6. Foi implementado um filtro média móvel eficiente para realizar um pré-processamento de dados de sensores, com o intuito de reduzir ruídos. E finalmente estes blocos foram integrados com um processador RISC-V, que é uma opção promissora de processador para realizar o controle de um SoC como esse. Estes blocos foram implementados em tecnologia CMOS e comparados com circuitos semelhantes na literatura, demonstrando resultados promissores.

**Palavras-chave:** RISC-V. IEEE 802.15.6. IoT.

# Abstract

Recent IoT systems require the integration of various functions like sensor reading, wireless communication, data processing and demand the execution of this tasks at a low power. A promising wireless communication technology for low power applications is the UWB, that allows for a considerable speed on the data transmission with low power. In order to implement this technology, a good practice is to follow the IEEE 802.15.6 standard for WBAN networks, that standardizes the implementation of UWB systems. This work has the goal of implementing a DSP system for controlling a SoC that transmits data via UWB. In order to do this, it was implemented the digital part of the physical layer of the UWB, as the standard IEEE 802.15.6 specifies. It was implemented an efficient simple moving average filter for the pre-processing of sensor data, with the goal of reducing noise on the data acquisition. And finally, these blocks were integrated with a RISC-V processor, which is a promising processor for controlling of a SoC like this. These blocks were implemented using CMOS and were compared with similar circuits available on literature, showing promising results.

**Keywords:** RISC-V. IEEE 802.15.6. IoT.

# Listas de ilustrações

|                                                                                                                                              |    |

|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 1 – Diagrama de blocos da arquitetura do SoC.                                                                                         | 15 |

| Figura 2 – Estrutura da mensagem do UWB.                                                                                                     | 18 |

| Figura 3 – Estrutura da mensagem expandida. (MANCHI; PAILY; GOGOI, 2017)                                                                     | 19 |

| Figura 4 – SHR header. (IEEE..., 2012)                                                                                                       | 20 |

| Figura 5 – Sequência kasami. (IEEE..., 2012)                                                                                                 | 20 |

| Figura 6 – Construção do $S_i$ . (IEEE..., 2012)                                                                                             | 21 |

| Figura 7 – Construção do PHR. (IEEE..., 2012)                                                                                                | 21 |

| Figura 8 – Construção do PSDU. (IEEE..., 2012)                                                                                               | 22 |

| Figura 9 – Seleção da semente do scrambler. (IEEE..., 2012)                                                                                  | 22 |

| Figura 10 – Arquitetura de um multiplicador em base canônica. (ZHANG, 2016)                                                                  | 27 |

| Figura 11 – Blocos do <i>PicoRV32</i> , disponível em (PICORV32..., 2025)                                                                    | 35 |

| Figura 12 – Diagrama Y de graus de abstração (WESTE; HARRIS, 2015)                                                                           | 40 |

| Figura 13 – Fluxo de Projeto Digital                                                                                                         | 42 |

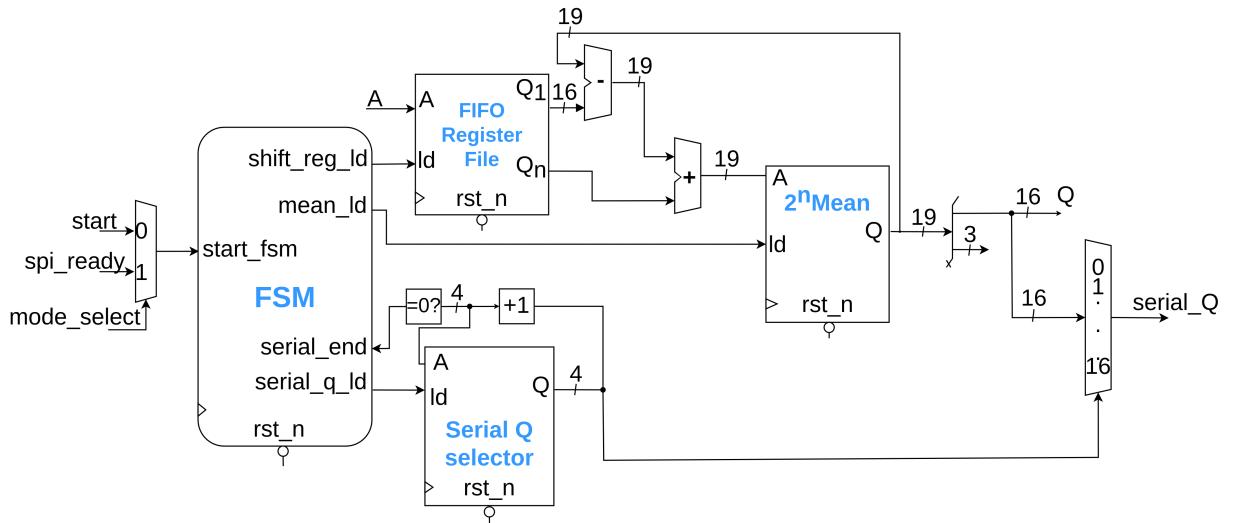

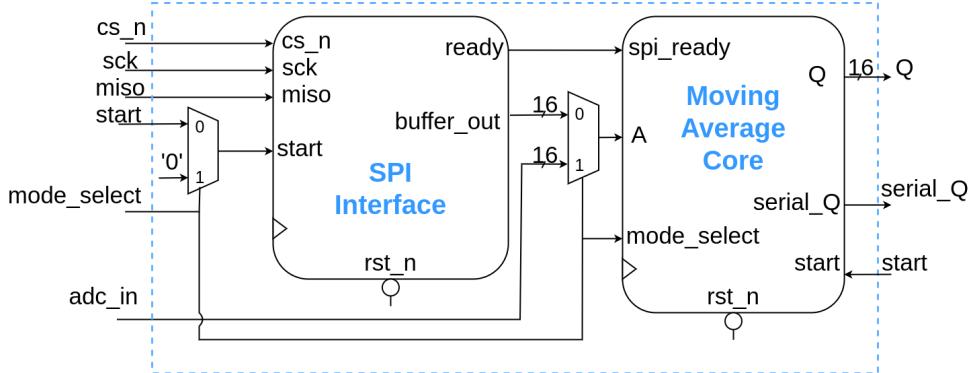

| Figura 14 – Diagrama de blocos para o circuito do filtro de média móvel simples.                                                             | 50 |

| Figura 15 – Arquitetura do protótipo inicial do filtro média móvel.                                                                          | 51 |

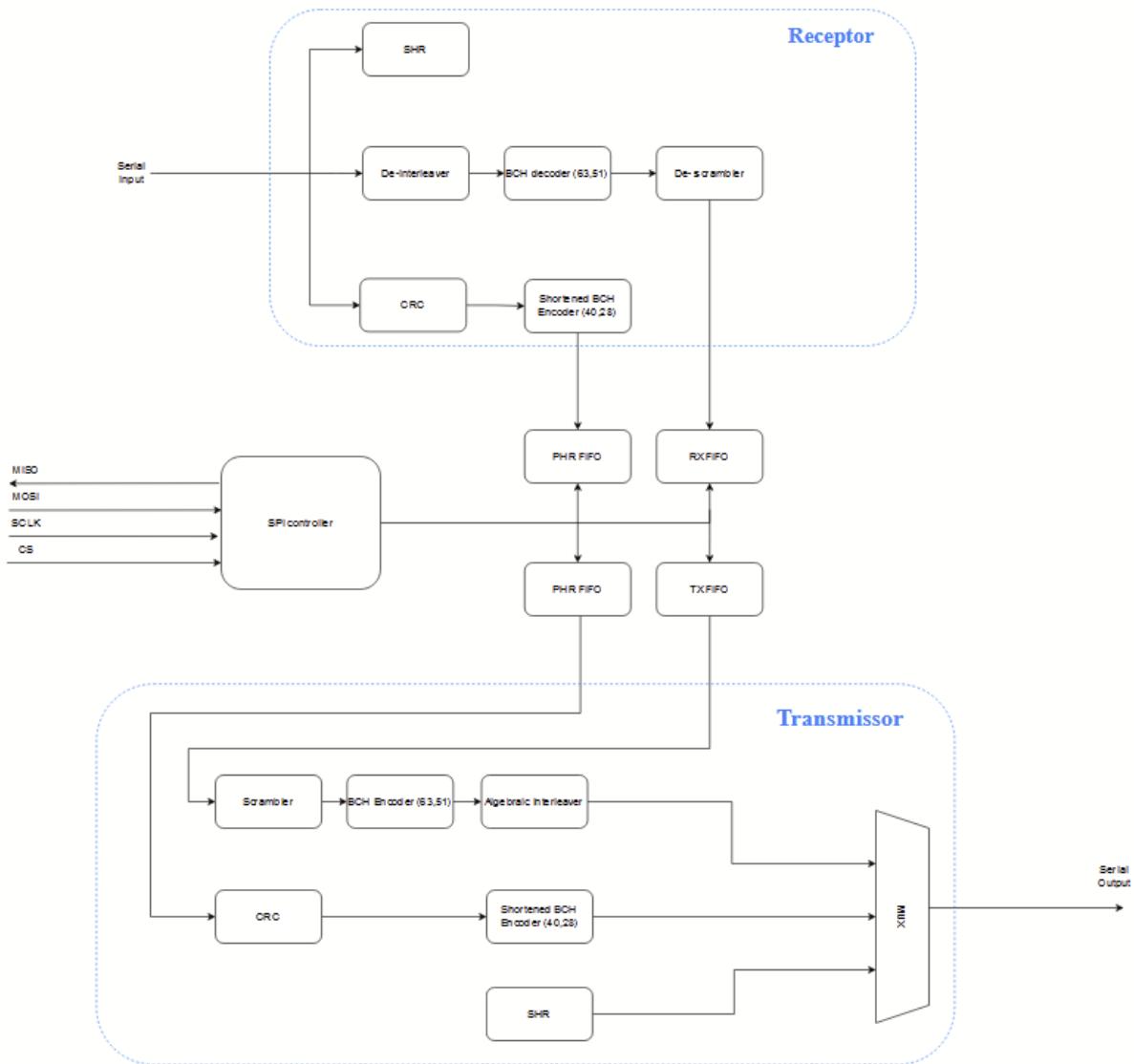

| Figura 16 – Diagrama de blocos do circuito proposto para implementar a camada física do UWB, seguindo o padrão IEEE 802.15.6                 | 52 |

| Figura 17 – Circuito para o <i>scrambler</i> . (IEEE..., 2012)                                                                               | 53 |

| Figura 18 – Codificador BCH (ZHANG, 2016)                                                                                                    | 54 |

| Figura 19 – Circuito de cálculo serial das síndromes. (ZHANG, 2016)                                                                          | 56 |

| Figura 20 – Circuito <i>Chien Search</i> . (ZHANG, 2016)                                                                                     | 57 |

| Figura 21 – Circuito LFSR para realizar o HCS. (IEEE..., 2012)                                                                               | 57 |

| Figura 22 – Máquina de estados para checar sequência do SHR                                                                                  | 58 |

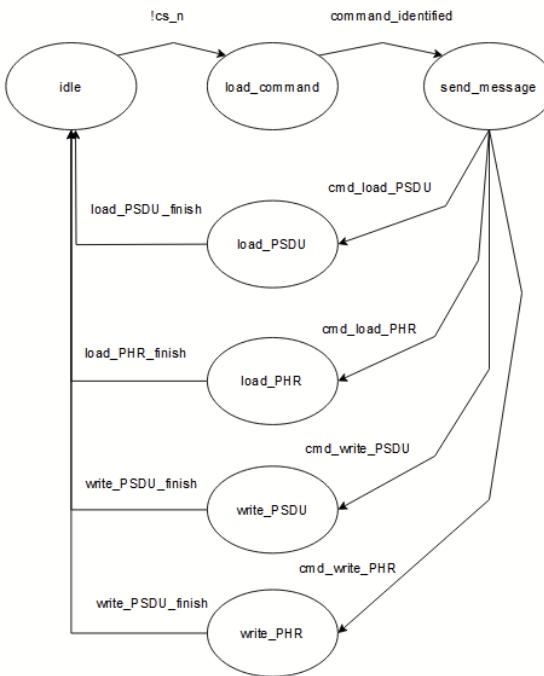

| Figura 23 – Máquina de estados do controlador SPI                                                                                            | 59 |

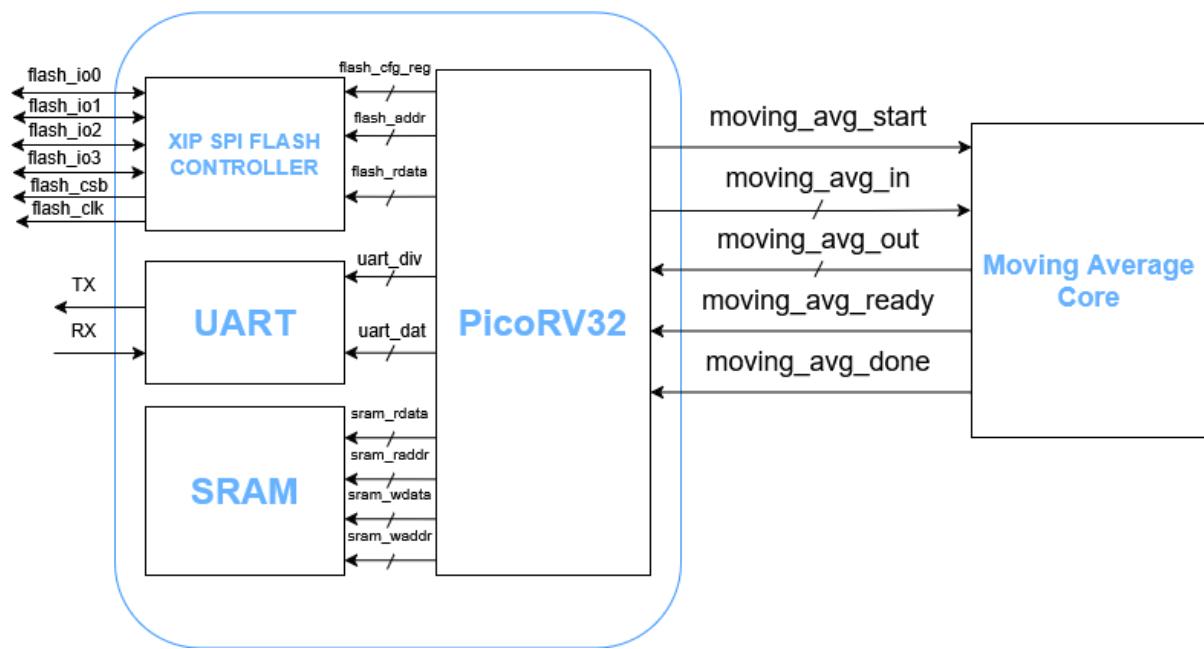

| Figura 24 – Diagrama de blocos da integração entre o RISC-V e o filtro média móvel.                                                          | 60 |

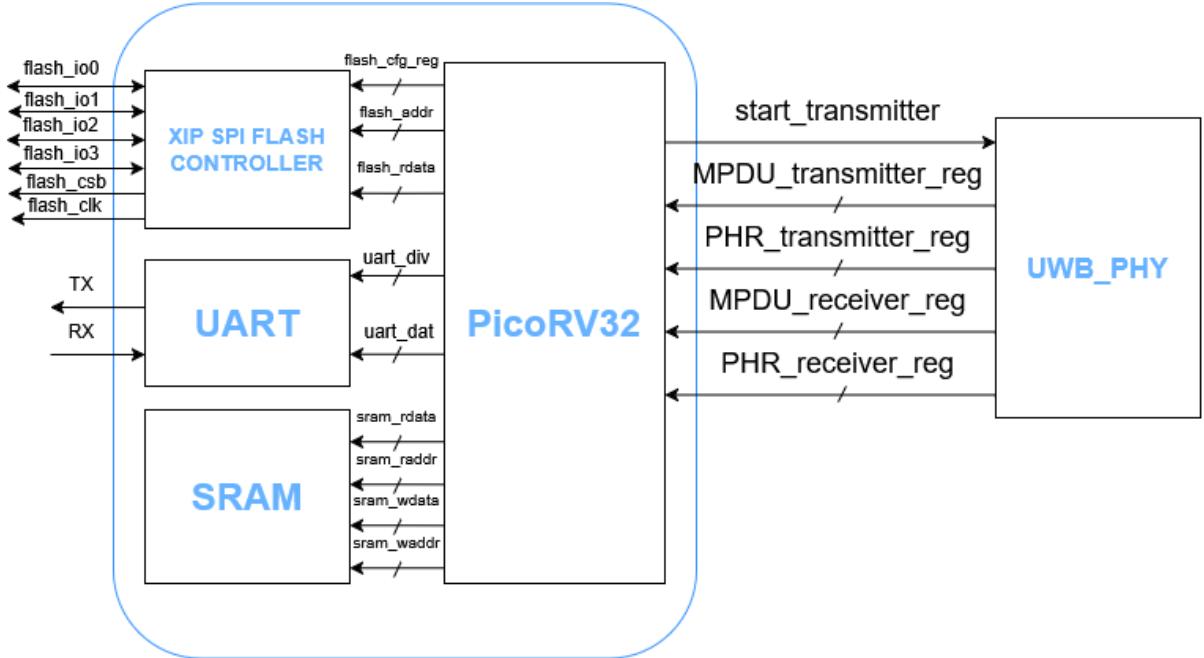

| Figura 25 – Diagrama de blocos da integração entre o RISC-V e a implementação da camada física para o UWB.                                   | 61 |

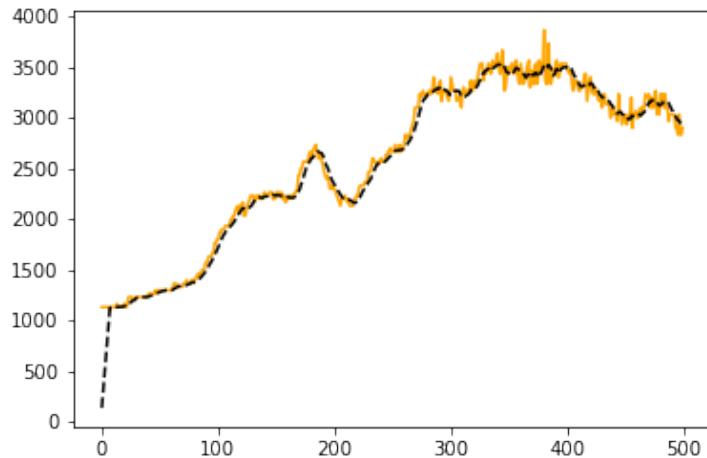

| Figura 26 – Simulação do filtro média móvel. O eixo x representa o tempo da simulação e o eixo y representa o valor de entrada e saída.      | 65 |

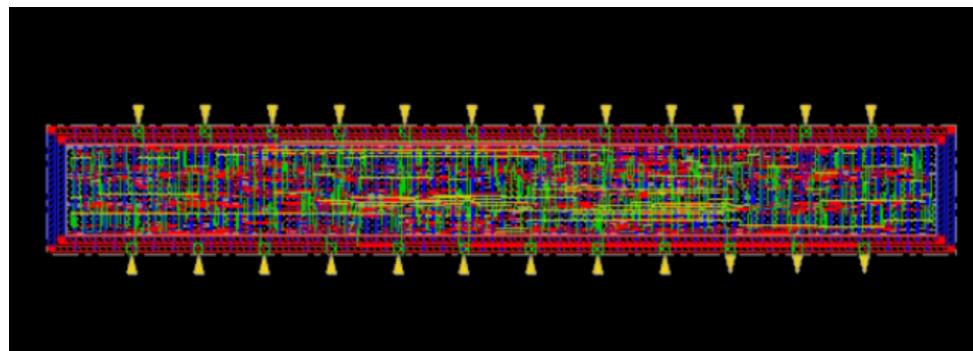

| Figura 27 – Layout do bloco implementado em tecnologia CMOS 180nm.                                                                           | 65 |

| Figura 28 – Resultado do <i>timing</i> para o filtro média móvel. Tempo em nanossegundos e a frequência do <i>clock</i> simulado é de 1 MHz. | 65 |

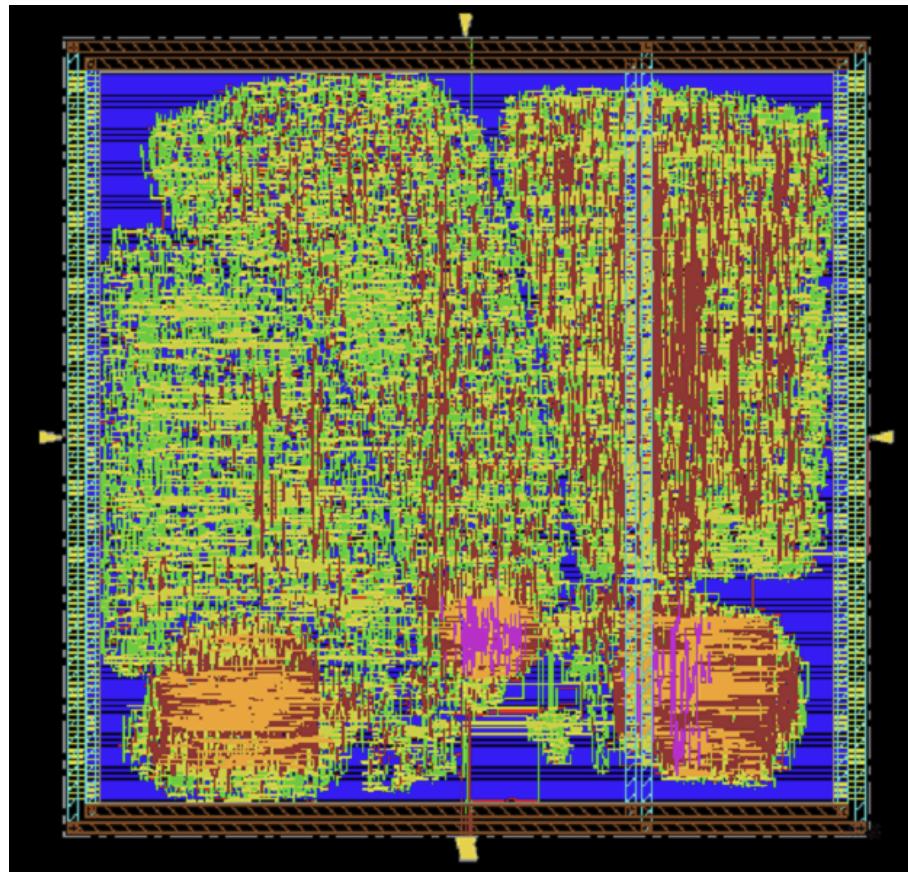

| Figura 29 – Layout final do processador em banda base                                                                                        | 69 |

| Figura 30 – Resultado de <i>timing</i> do circuito. Tempo em nanossegundos e a frequência do <i>clock</i> simulado é de 487,5 kHz.           | 69 |

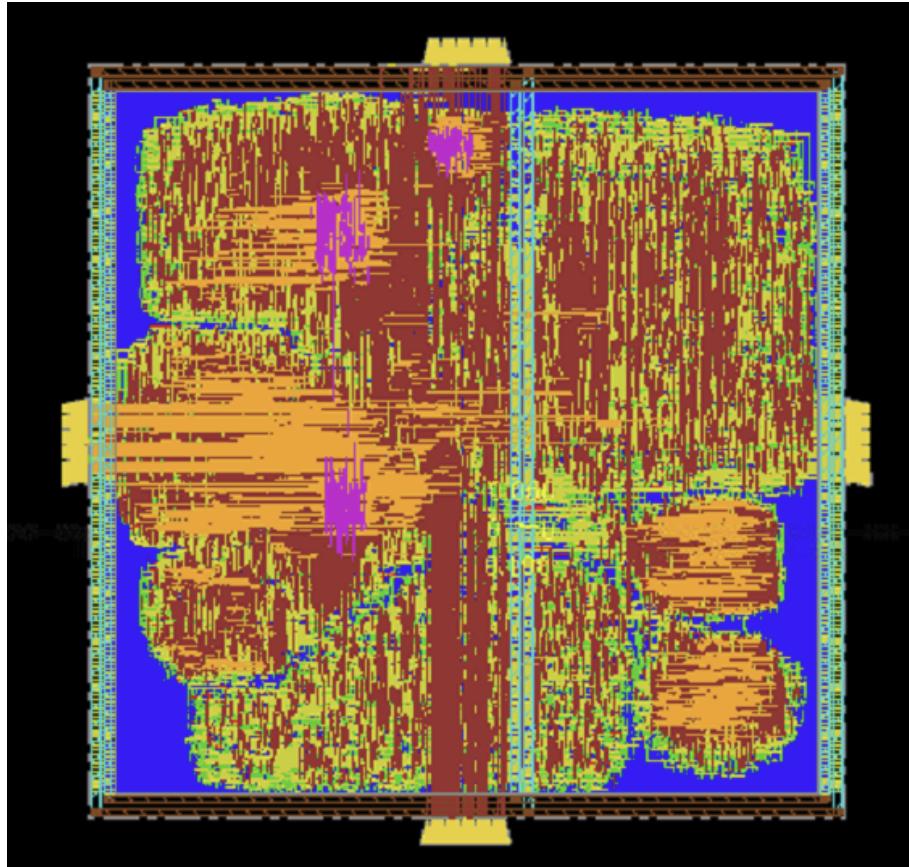

| Figura 31 – Layout final do circuito                                                                                                         | 70 |

|                                                                                                                                                       |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 32 – Resultados de <i>timing</i> do <i>picosoc</i> . Tempo em nanossegundos e a frequência<br>do <i>clock</i> simulado é de 487,5 kHz. . . . . | 71 |

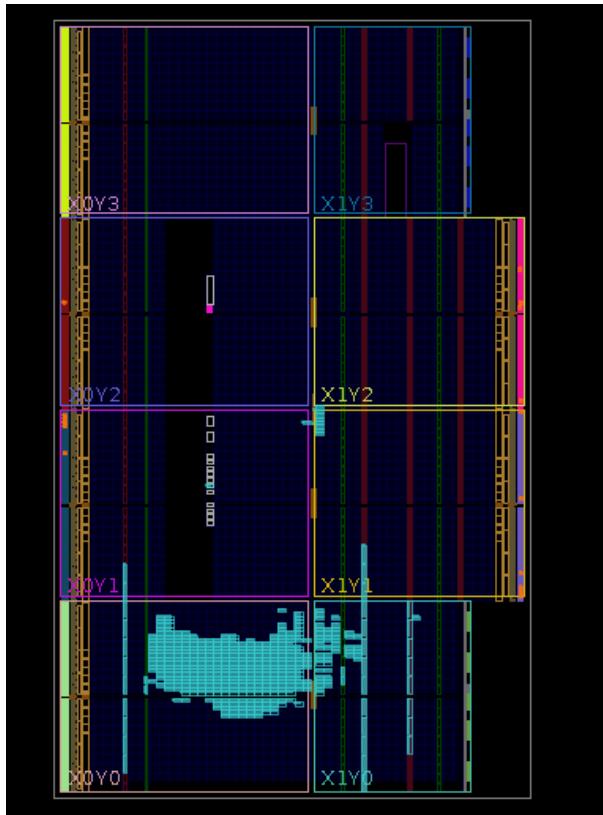

| Figura 33 – Layout FPGA, <i>picosoc</i> + SMA . . . . .                                                                                               | 78 |

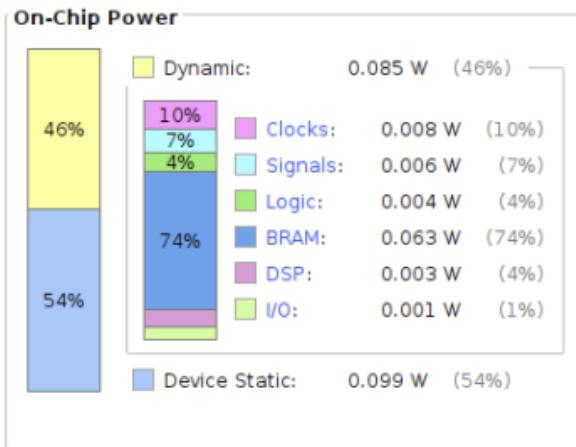

| Figura 34 – Consumo de potência do RISC-V + Média Móvel . . . . .                                                                                     | 79 |

| Figura 35 – Consumo de recursos do RISC-V + Média Móvel . . . . .                                                                                     | 79 |

| Figura 36 – Resultados de <i>timing</i> para o RISC-V + Média Móvel . . . . .                                                                         | 79 |

# **Lista de tabelas**

|                                                                                                                 |    |

|-----------------------------------------------------------------------------------------------------------------|----|

| Tabela 1 – Exemplos de extensões base possíveis para uma implementação do <i>RISC-V</i> . . . . .               | 33 |

| Tabela 2 – Exemplos de extensões possíveis para uma implementação do <i>RISC-V</i> . . . . .                    | 34 |

| Tabela 3 – Lista de portas do circuito de filtro média móvel e a descrição de suas<br>funcionalidades . . . . . | 51 |

| Tabela 4 – Lista de portas do circuito de camada física UWB e a descrição de suas<br>funcionalidades . . . . .  | 52 |

| Tabela 5 – Consumo de energia, área e células para o filtro média móvel (1 MHz) . . . . .                       | 66 |

| Tabela 6 – Comparação de área e potência com outras implementações de filtro FIR . . . . .                      | 66 |

| Tabela 7 – Consumo de energia, área e células . . . . .                                                         | 69 |

| Tabela 8 – Comparação de potência entre transceptores UWB disponíveis na literatura . . . . .                   | 71 |

| Tabela 9 – Comparação de consumo de área entre transceptores UWB disponíveis<br>na literatura . . . . .         | 72 |

| Tabela 10 – Consumo de recursos do protótipo em FPGA do filtro média móvel . . . . .                            | 77 |

| Tabela 11 – Consumo de energia do protótipo em FPGA do filtro média móvel . . . . .                             | 77 |

# Sumário

|            |                                                   |           |

|------------|---------------------------------------------------|-----------|

| <b>1</b>   | <b>INTRODUÇÃO . . . . .</b>                       | <b>14</b> |

| <b>1.1</b> | <b>Objetivos Geral e Específicos . . . . .</b>    | <b>15</b> |

| <b>1.2</b> | <b>Contribuições do Trabalho . . . . .</b>        | <b>16</b> |

| <b>1.3</b> | <b>Organização do Trabalho . . . . .</b>          | <b>16</b> |

| <b>2</b>   | <b>FUNDAMENTAÇÃO TEÓRICA . . . . .</b>            | <b>17</b> |

| <b>2.1</b> | <b>Filtro FIR e Média Móvel Simples . . . . .</b> | <b>17</b> |

| <b>2.2</b> | <b>Padrão IEEE 802.15.6 . . . . .</b>             | <b>17</b> |

| 2.2.1      | SHR . . . . .                                     | 20        |

| 2.2.2      | PHR . . . . .                                     | 21        |

| 2.2.3      | PSDU . . . . .                                    | 21        |

| <b>2.3</b> | <b>Corpos Finitos(Corpos de Galois) . . . . .</b> | <b>23</b> |

| 2.3.1      | Corpo . . . . .                                   | 23        |

| 2.3.2      | Ordem de um elemento . . . . .                    | 24        |

| 2.3.3      | Elemento primitivo . . . . .                      | 24        |

| 2.3.4      | Polinômio Irreduzível . . . . .                   | 24        |

| 2.3.5      | Polinômio Primitivo . . . . .                     | 24        |

| 2.3.6      | Polinômio Mínimo . . . . .                        | 24        |

| 2.3.7      | Base canônica . . . . .                           | 25        |

| <b>2.4</b> | <b>Aritmética em Corpos Finitos . . . . .</b>     | <b>25</b> |

| 2.4.1      | Soma . . . . .                                    | 25        |

| 2.4.2      | Subtração . . . . .                               | 26        |

| 2.4.3      | Multiplicação . . . . .                           | 26        |

| <b>2.5</b> | <b>BCH . . . . .</b>                              | <b>28</b> |

| 2.5.1      | Decodificação BCH . . . . .                       | 29        |

| 2.5.2      | Síndromes . . . . .                               | 30        |

| 2.5.3      | Algoritmo de Peterson . . . . .                   | 30        |

| 2.5.4      | Chien Search . . . . .                            | 32        |

| <b>2.6</b> | <b>RISC-V . . . . .</b>                           | <b>32</b> |

| 2.6.1      | PicoRV32 . . . . .                                | 34        |

| 2.6.2      | PicoSoC . . . . .                                 | 34        |

| <b>2.7</b> | <b>Estado da Arte . . . . .</b>                   | <b>35</b> |

| <b>3</b>   | <b>ASPECTOS METODOLÓGICOS . . . . .</b>           | <b>38</b> |

| <b>3.1</b> | <b>Níveis de Abstração . . . . .</b>              | <b>38</b> |

| <b>3.2</b> | <b>Fluxo de projeto Digital . . . . .</b>         | <b>41</b> |

|             |                                                        |           |

|-------------|--------------------------------------------------------|-----------|

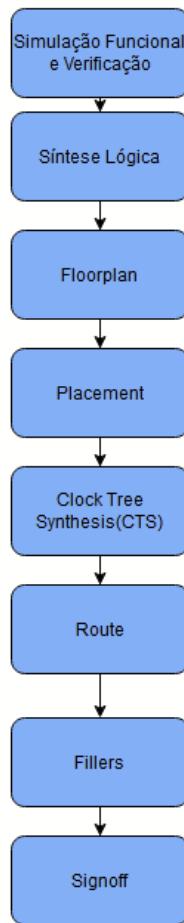

| 3.2.1       | <i>Hardware Description Language (HDL)</i> . . . . .   | 41        |

| 3.2.2       | Simulação Funcional e Verificação . . . . .            | 42        |

| 3.2.3       | Síntese Lógica . . . . .                               | 43        |

| 3.2.4       | <i>Floorplan</i> . . . . .                             | 43        |

| 3.2.5       | Placement . . . . .                                    | 44        |

| 3.2.6       | <i>Clock Tree Synthesis</i> . . . . .                  | 44        |

| 3.2.7       | <i>Route</i> . . . . .                                 | 45        |

| 3.2.8       | <i>Fillers</i> . . . . .                               | 45        |

| 3.2.9       | Verificações Finais ( <i>Signoff</i> ) . . . . .       | 45        |

| 3.2.10      | PDK . . . . .                                          | 46        |

| 3.2.11      | Especifidades do projeto . . . . .                     | 46        |

| <b>3.3</b>  | <b>Figuras de Mérito</b> . . . . .                     | <b>46</b> |

| 3.3.1       | <i>Gate Equivalent (GE)</i> . . . . .                  | 47        |

| 3.3.2       | Adaptação para o GE . . . . .                          | 47        |

| 3.3.3       | Potência Normalizada . . . . .                         | 47        |

| <b>4</b>    | <b>PROPOSTA DE CIRCUITOS</b> . . . . .                 | <b>49</b> |

| <b>4.1</b>  | <b>Filtro de Média Móvel Simples</b> . . . . .         | <b>49</b> |

| 4.1.1       | Arquitetura do filtro para protótipo inicial . . . . . | 50        |

| <b>4.2</b>  | <b>Camada física do UWB (IEEE 802.15.6)</b> . . . . .  | <b>51</b> |

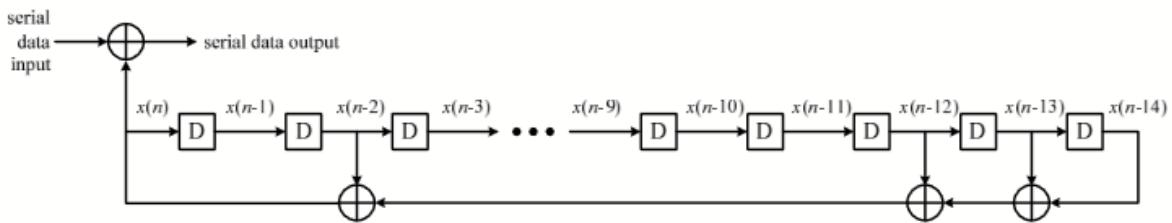

| <b>4.3</b>  | <b>Scrambler</b> . . . . .                             | <b>53</b> |

| <b>4.4</b>  | <b>De-Scrambler</b> . . . . .                          | <b>54</b> |

| <b>4.5</b>  | <b>Interleaver</b> . . . . .                           | <b>54</b> |

| <b>4.6</b>  | <b>De-Interleaver</b> . . . . .                        | <b>54</b> |

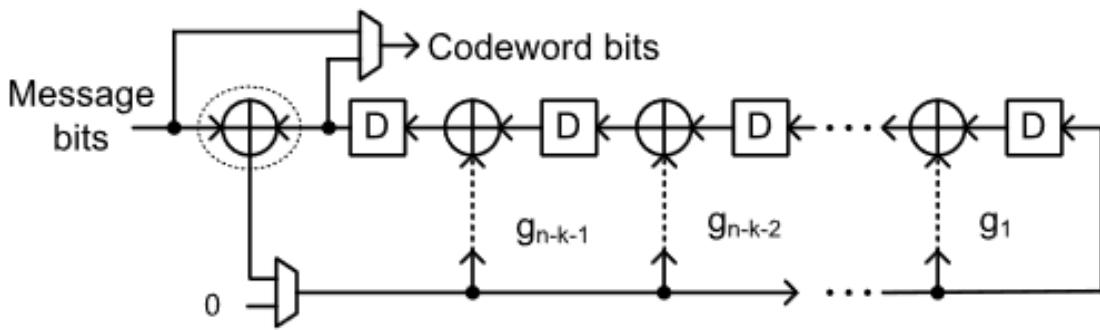

| <b>4.7</b>  | <b>Codificador BCH</b> . . . . .                       | <b>54</b> |

| <b>4.8</b>  | <b>Decodificador BCH</b> . . . . .                     | <b>55</b> |

| 4.8.1       | Cálculo das síndromes . . . . .                        | 55        |

| 4.8.2       | <i>Key Equation Solver</i> . . . . .                   | 56        |

| 4.8.3       | <i>Chien Search</i> . . . . .                          | 56        |

| <b>4.9</b>  | <b>BCH encurtado para o PHR</b> . . . . .              | <b>57</b> |

| <b>4.10</b> | <b>Header Check Sequence</b> . . . . .                 | <b>57</b> |

| <b>4.11</b> | <b>SHR(Receptor)</b> . . . . .                         | <b>58</b> |

| <b>4.12</b> | <b>SHR(Transmissor)</b> . . . . .                      | <b>58</b> |

| <b>4.13</b> | <b>Controlador SPI</b> . . . . .                       | <b>59</b> |

| <b>4.14</b> | <b>Integração com RISC-V</b> . . . . .                 | <b>60</b> |

| <b>5</b>    | <b>RESULTADOS E DISCUSSÃO</b> . . . . .                | <b>63</b> |

| <b>5.1</b>  | <b>Média móvel simples</b> . . . . .                   | <b>63</b> |

| 5.1.1       | Simulação do código HDL . . . . .                      | 63        |

| 5.1.2       | Síntese Física . . . . .                               | 64        |

|            |                                             |           |

|------------|---------------------------------------------|-----------|

| <b>5.2</b> | <b>Processador banda base UWB</b>           | <b>66</b> |

| 5.2.1      | Simulação                                   | 66        |

| 5.2.2      | Síntese física                              | 68        |

| 5.2.3      | Integração com RISC-V                       | 70        |

| <b>6</b>   | <b>CONCLUSÃO</b>                            | <b>73</b> |

|            | <b>REFERÊNCIAS</b>                          | <b>74</b> |

|            | <b>APÊNDICE A – IMPLEMENTAÇÕES EM FPGA</b>  | <b>77</b> |

| A.1        | Implementação do Filtro Média móvel em FPGA | 77        |

| A.2        | Integração do filtro com RISC-V em FPGA     | 77        |

# 1 Introdução

Internet das Coisas (*IoT - Internet of Things*) é uma rede de dispositivos equipados com sensores e sistemas de comunicação que permitem a transmissão e recepção de dados. Um exemplo é a tecnologia emergente conhecida como WBAN (*Wireless Body Area Network*), que consiste em um conjunto de nós que possibilita a aquisição contínua de sinais fisiológicos por meio de biossensores que podem ser anexados ou até mesmo implantados no corpo. Os dados coletados podem ser transmitidos para médicos ou armazenados em bancos de dados. Assim, é possível realizar o monitoramento de pacientes em tempo real, o que facilita a realização de diagnósticos e intervenções médicas quando necessário.

Nesse contexto, encontra-se em desenvolvimento na Universidade de Brasília um SoC (*System-on-Chip*) baseado na arquitetura RISC-V com o objetivo de monitorar e processar sinais biológicos a partir de sensores, e realizar a transmissão e recepção de dados por meio da tecnologia UWB (*Ultra-Wideband*). Essa tecnologia oferece vantagens relevantes para este tipo de aplicação por apresentar um consumo baixo de energia, já que o envio de dados é feito por pulsos curtos de transmissão, e por utilizar uma banda larga, o que possibilita uma taxa alta de transmissão de dados. Além disso, essa tecnologia não necessita de uma portadora para a transmissão de dados, operando assim em banda base.

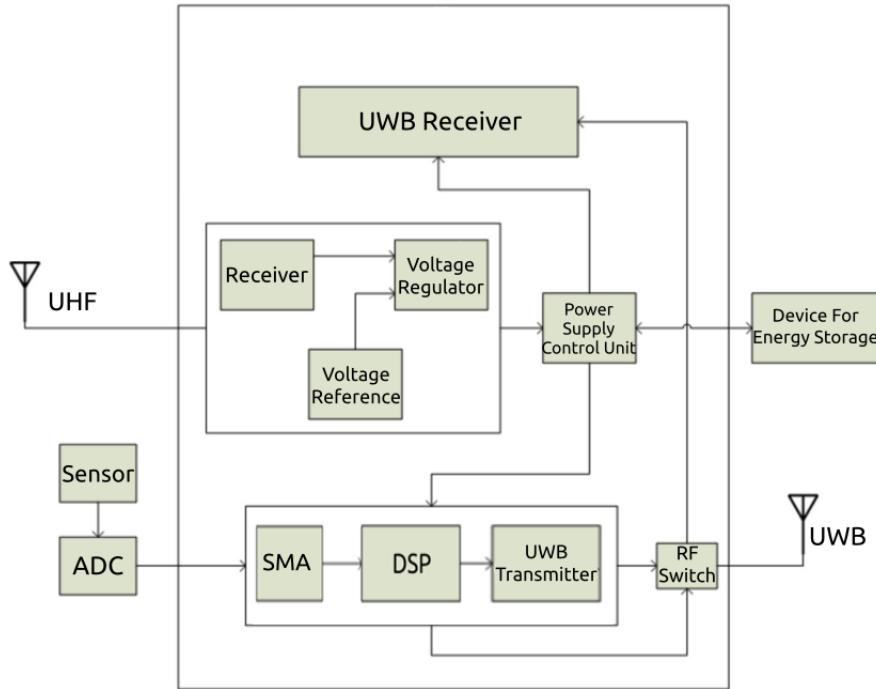

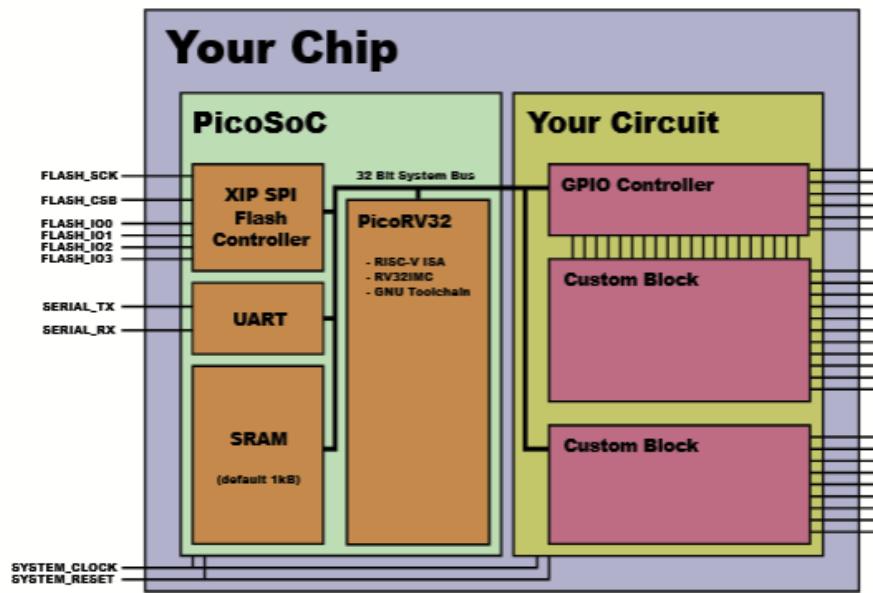

A arquitetura do SoC, mostrada na Figura 1, é adaptável e permite uma integração perfeita em aplicações WBAN, atuando como nó em uma rede de sensores sem fio. A antena UHF (*Ultra High Frequency*) alimenta o sistema de gerenciamento de energia, que recebe o sinal e o converte em uma tensão apropriada para o sistema, além de armazenar a energia na bateria. A antena UWB recebe e transmite dados, sendo estas funções selecionadas pelo *RF Switch* (comutador RF). O SoC recebe dados de um sensor, que é seguido de um conversor analógico para digital que enviará os dados convertidos para um DSP (*Digital Signal Processor*). Entre o DSP e o ADC (*Analog to Digital Converter*) há um bloco SMA (*Simple Moving Average*), que consiste em um filtro para retirar ruídos dos sinais recebidos do sensor, antes serem processados no DSP.

O uso de um DSP permite processar e selecionar os dados recebidos do sensor de tal forma que não seja necessário transmitir uma grande quantidade de informação. Isso promove uma maior eficiência energética, pois a transmissão de dados em sistemas IoT é uma grande fonte de consumo energético. Desse modo, processar os dados antes de serem transmitidos pode ser uma oportunidade para promover uma maior eficiência energética.

O bloco DSP será composto por uma microarquitetura especificamente projetada para tarefas de processamento de sinais digitais, garantindo ao mesmo tempo eficiência energética. A ISA (*Instruction Set Architecture*) RISC-V foi escolhida porque é composta por um conjunto

Figura 1 – Diagrama de blocos da arquitetura do SoC.

básico de instruções que pode ser adaptado e otimizado para as necessidades específicas da aplicação. Uma implementação adequada é o PicoRV32, um núcleo de microcontrolador simples que permite diferentes configurações e é aberto sob a licença ISC. Esse bloco também será responsável pela implementação da camada física do transceptor UWB, que enquadra a mensagem a ser transmitida em um quadro de comunicação adequado para a tecnologia. É na camada física que são implementadas as operações que inserem bits de verificação na mensagem e permitem a correção de erros, bem como as operações de embaralhamento da mensagem que promovem segurança e uma distribuição melhor do espectro potência do sinal.

## 1.1 Objetivos Geral e Específicos

O objetivo geral deste trabalho é desenvolver e implementar em ASIC dois blocos digitais para o SoC: o filtro média móvel e a camada física do transceptor UWB conforme a norma IEEE 802.15.6. Para isso, foram listados os seguintes objetivos específicos:

- Especificação de um filtro média móvel para filtrar o sinal de um sensor.

- Especificação de um bloco dedicado que implementa a camada física do transceptor UWB conforme a norma IEEE 802.15.6.

- Codificação dos blocos em *Verilog* e validação por meio de simulações.

- Integração dos blocos com o *PicoRV32* e validação por meio de simulações.

- e) Execução do fluxo digital para sínteses lógica e física, com geração e verificação dos layouts.

- f) Caracterização dos circuitos a partir de dados de consumo energético, área e atraso.

## 1.2 Contribuições do Trabalho

Dentre as contribuições deste trabalho, destacam-se as listadas abaixo:

- a) Circuito do filtro média móvel enviado para *tape-out* e fabricado na tecnologia CMOS UMC 180nm, com artigo publicado em conferência ([SANTOS, 2023](#)).

- b) Proposta de uma arquitetura para o processamento em banda-base que utiliza aritmética em corpos finitos.

- c) Integração dos blocos ao PicoRV32.

## 1.3 Organização do Trabalho

Este trabalho está organizado da seguinte forma: o capítulo 2 contém o estado da arte e a fundamentação teórica, na qual são explicados todos os fundamentos importantes para a compreensão deste trabalho; no capítulo 3, o fluxo de desenvolvimento utilizado neste trabalho foi detalhado; no capítulo 4, foram apresentadas as propostas de circuito para cada um dos blocos; no capítulo 5, os resultados da implementação dos circuito propostos foram discutidos, sendo apresentados dados de consumo de área, potência e desempenho; por fim, as conclusões foram apresentadas no capítulo 6.

## 2 Fundamentação teórica

### 2.1 Filtro FIR e Média Móvel Simples

Um filtro de resposta finita ao impulso (FIR) é um filtro baseado no modelo FIR que é um modelo com entradas exógenas, que pode ser expressado pela equação 2.1 (BILLINGS, 2013):

$$y(k) = b_1 u(k-1) + b_2 u(k-2) + \dots + b_n u(k-n) \quad (2.1)$$

onde  $u$  representa a entrada do filtro, e  $b_i$  são os parâmetros do filtro. Esse tipo de filtro funciona de forma a realizar uma operação de soma ponderada de  $n$  amostras da entrada, funcionando efetivamente como um filtro passa-baixas. Desta forma, ele atenua componentes de alta frequência no sinal de entrada e tem diversas aplicações em várias áreas (ALJUFFRI et al., 2015) (ANNANGI; PULI, 2017) (CHAUHAN et al., 2018) (MORALES-MENDOZA et al., 2008).

Um filtro Média Móvel Simples (SMA) é um caso particular de filtros FIR em que todos os parâmetros são iguais e a soma destes é igual a 1. A equação 2.2 mostra o modelo matemático deste filtro.

$$y(k) = \frac{u(k-1) + u(k-2) + u(k-3) + \dots + u(k-n)}{n} \quad (2.2)$$

Embora filtros de média móvel simples não tenham a versatilidade de um filtro FIR, ainda sim, eles tem alto valor prático em diversas aplicações, como mostra (MUÑOZ et al., 2017; PASTRANA et al., 2022). Um exemplo do uso de filtros de média móvel simples é o uso em sensores ruidosos para obter leituras mais estáveis. Em um estudo conduzido por (MAGSI et al., 2018), vários filtros são analisados e a efetividade da redução de ruído é avaliada através de simulações. Os resultados indicam que o filtro é capaz de reduzir até 95% do ruído. Esse resultado sugere que filtros de média móvel simples tem uma boa performance na redução de ruídos de alta frequência, de modo que esta pode ser uma ferramenta relevante para a redução de ruídos.

### 2.2 Padrão IEEE 802.15.6

O padrão IEEE 802.15.6, é uma norma que foi criada com o objetivo de padronizar a comunicação sem fio de aparelhos que se enquadram na categoria de redes BAN (*Body Area Network*). Essa categoria é voltada a aparelhos vestíveis sendo em alguns casos equipamentos

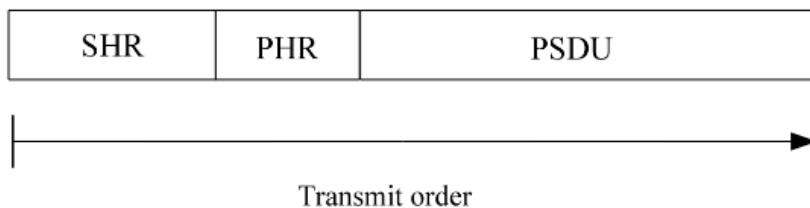

Figura 2 – Estrutura da mensagem do UWB.

com aplicações médicas. Nesta categoria a comunicação ocorre em curto alcance, ocorrendo dentro de um corpo humano (não limitado a humanos), ou na vizinhança próxima deste.

Dado esta aplicação, este padrão oferece formas de comunicação que utiliza bandas de frequência que sejam aplicáveis para aplicações médicas. Também permite que os aparelhos comuniquem em baixa potência, de modo a otimizar o consumo de bateria e minimizar a energia eletromagnética que pode ser absorvida pelo corpo humano. E também oferece segurança na transmissão dos dados, de modo que se proteja comunicações que carreguem dados sensíveis.

Este padrão define a camada física, e a subcamada de MAC (*Medium Access Control*), que é complementar, e serve para construir os quadros de comunicação a serem enviados pela camada física. Também neste padrão são especificados 3 tipos de camada física (PHY), o *Narrowband* (NB) , o *Ultra Wide Band* (UWB) e o *Human body Communications* (HBC).

Para o presente trabalho, iremos focar na camada física do UWB, de modo que a camada de MAC fica fora do escopo deste projeto, assim como o NB e o HBC. Além disso focaremos nas etapas de processamento digital que precedem os circuitos analógico e de RF responsáveis pela transmissão das mensagens.

Para transmitir uma mensagem por UWB, a norma define uma estrutura padrão que deve ser seguida, sendo que cada uma das partes da estrutura terá particularidades na implementação. Na figura 2 as 3 partes principais de uma mensagem UWB estão representadas.

O SHR (*Synchronization Header*) é o cabeçalho de sincronização. Neste cabeçalho, uma sequência de bits é enviada repetidas vezes, e tem o objetivo de sinalizar que uma mensagem está chegando e oferecer uma forma de que o circuito possa se sincronizar com a transmissão.

O PHR (*Physical layer Header*) é o cabeçalho de camada física. Esse cabeçalho traz informações sobre a mensagem que está sendo enviada, como o tamanho do corpo da mensagem e a taxa de transmissão dos dados.

O PSDU (*Physical layer Service Data Unit*) é o corpo da mensagem. Nessa seção da mensagem, é incluso o quadro de comunicação que vem do MAC, que é chamado de MPDU. Esse quadro contém o corpo da mensagem, um cabeçalho do MAC, e bits de paridade.

Figura 3 – Estrutura da mensagem expandida. ([MANCHI; PAILY; GOGOI, 2017](#))

Na figura 3 uma visão expandida da mensagem é apresentada. Na imagem é possível ver o PHR (Na imagem PLCP Header), que é construído do cabeçalho propriamente dito, mais bits de CRC e bits de paridade BCH. Estes bits servem como uma forma de checar a integridade da mensagem. Sendo que com os bits de CRC é possível checar se a mensagem do cabeçalho está íntegra e o BCH também tem essa função, porém a partir do BCH, não só é possível verificar erros na mensagem como pode-se corrigir a mensagem automaticamente, até uma quantidade máxima de bits trocados. Mais detalhes sobre ambos o CRC e BCH serão apresentados em seções posteriores.

Também na figura 3 é possível ver a estrutura do PHR. Ele contém 24 bits, sendo os 3 primeiros apresentados na imagem como "Rate", estes são os bits reservados para especificar a taxa de transmissão da mensagem. Todos os espaços preenchidos com a letra "r" são espaços reservados e não carregam informação a priori. O espaço "Length" se refere a 8 bits reservados para definir o tamanho do corpo da mensagem bytes, podendo variar entre 0 bytes até 255 bytes. O "B" é o "burst mode" que é um bit usado para definir se a mensagem está sendo enviada em modo *burst* ou não. Esse modo permite que se envie vários pacotes consecutivos sem precisar que o receptor envie uma mensagem de resposta, confirmando o correto recebimento da mensagem. "Pulse type" é um bit que define qual tipo de pulso deve ser usado na transmissão. O HARQ são dois bits que controlam o estado do HARQ, que é um fluxo de retransmissão. "SS" é uma semente para o *scrambler*, que é um bloco que será detalhado mais adiante. E finalmente o "km" define qual será a constelação utilizada.

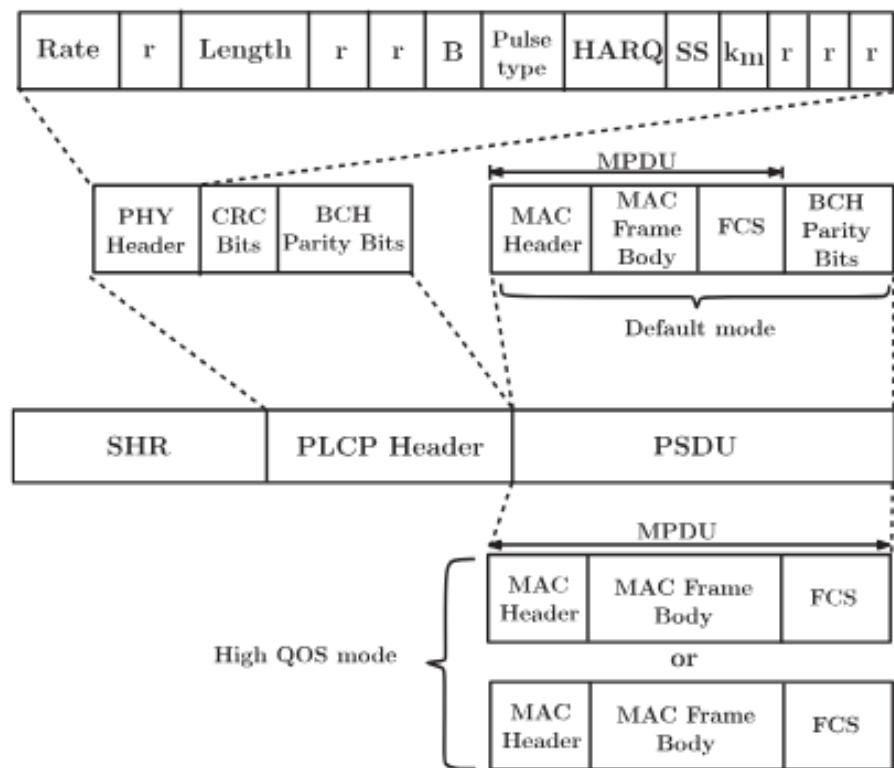

Figura 4 – SHR header. (IEEE..., 2012)

|                      |                                                                                                                               |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------|

| <b>C<sub>1</sub></b> | 1 1 1 1 1 1 0 1 0 1 0 1 1 0 0 1 1 0 1 1 1 0 1 1 0 1 0 0 1 0 0 1 1 1 0 0 0 1 0 1 1 1 1 0 0 1 0 1 0 0 0 1 1 0 0 0 0 1 0 0 0 0 0 |

| <b>C<sub>2</sub></b> | 0 0 0 1 1 0 0 0 1 0 0 1 0 0 1 0 0 1 0 1 1 0 0 0 1 1 0 0 1 1 1 0 0 1 1 0 0 1 0 0 1 0 1 0 1 1 0 0 0 1 1 0 1 0 1 0 1 0 0 1 0     |

| <b>C<sub>3</sub></b> | 1 0 0 0 1 1 1 1 0 1 1 1 1 0 0 0 1 1 1 0 0 0 0 1 1 0 1 1 1 1 0 1 1 1 0 1 0 1 1 1 0 1 1 1 0 0 1 1 0 1 0 0 0 0 1 0 0 1 1 0 0 1   |

| <b>C<sub>4</sub></b> | 0 1 0 0 0 1 0 0 0 0 1 0 1 0 1 1 0 1 0 1 1 1 1 0 1 0 0 0 0 0 1 0 0 1 0 1 0 0 1 0 1 1 0 0 1 0 1 1 0 1 0 0 0 1 0 0 1 1 1 1 0 0   |

| <b>C<sub>5</sub></b> | 1 0 1 0 0 0 0 1 1 1 1 0 0 0 0 0 1 1 0 0 1 0 0 1 1 0 1 0 1 1 0 0 0 0 0 1 1 1 0 0 1 1 1 0 0 1 0 0 0 1 1 0 1 1 0 0 0 0 1 1 1 0   |

| <b>C<sub>6</sub></b> | 1 1 0 1 0 0 1 1 0 0 0 0 0 1 0 1 0 0 0 0 0 1 0 0 0 1 1 1 0 1 1 0 0 1 0 0 0 0 0 0 1 0 1 1 1 0 1 0 0 0 1 1 1 1 0 1 1 0 1 1 1     |

| <b>C<sub>7</sub></b> | 0 1 1 0 1 0 1 0 0 1 1 0 1 1 1 1 0 0 1 1 1 1 1 1 0 0 0 0 1 0 1 1 0 1 1 1 0 0 0 0 0 0 0 1 1 0 1 0 0 1 1 1 1 0 1 0 1 1 1         |

| <b>C<sub>8</sub></b> | 0 0 1 1 0 1 1 0 0 1 1 1 0 1 0 0 1 0 1 0 1 0 0 0 1 0 1 0 1 1 1 1 0 0 1 0 0 1 0 1 1 1 1 1 1 0 1 1 0 0 0 1 0 1                   |

Figura 5 – Sequência kasami. (IEEE..., 2012)

Para o PSDU pode-se ver na figura 3 a divisão do PSDU em um MPDU e os bits de paridade. O MPDU contém o cabeçalho MAC, tem o corpo do quadro do MAC, e contém o FCS(Frame Check Sequence) que são bits para verificar a integridade do quadro. O MPDU deve vir já formatado do MAC, com o formato adequado, para que seja transmitido pela camada física. O papel da camada física então é adicionar os bits de paridade BCH, que semelhante ao caso do PHR, servem para verificar a integridade da mensagem e permitem a correção automática da mensagem, dentro de um limite de bits trocados.

A seguir um pouco mais de detalhes sobre cada uma das seções da mensagem serão apresentados.

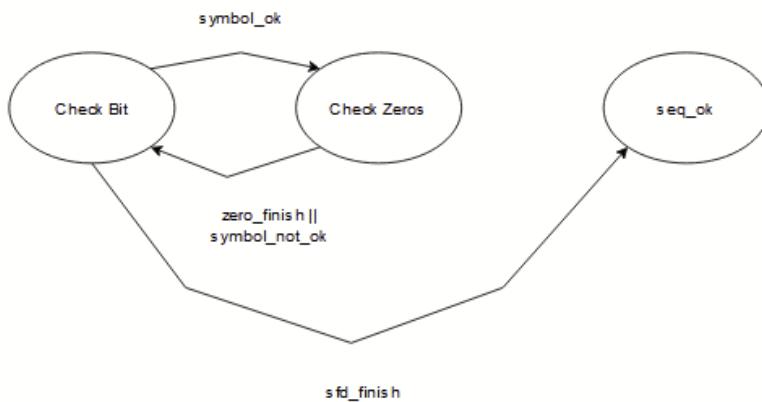

### 2.2.1 SHR

O SHR é dividido em 2 partes, o preâmbulo e o SFD (*Start-of-frame delimiter*). O preâmbulo serve para sincronização temporal e detecção de pacotes. A segunda parte serve para sincronizar quadro e delimita o começo deste.

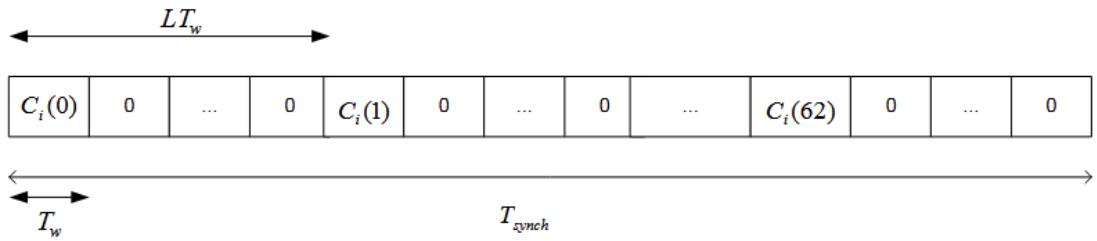

Para construir o preâmbulo são utilizadas sequências Kasami de tamanho 63. Há 8 sequências que são definidas na figura 5

O preâmbulo deve consistir em 4 repetições do símbolo  $S_i$ , sendo que o símbolo  $S_i$  é a sequência Kasami, porém com uma quantidade de bits '0' entre cada um dos bits da sequência. Então envia-se um bit, depois envia-se zeros, depois envia-se outro bit, envia-se outra quantidade de zeros, até acabar a sequência. A imagem 6 ilustra esta operação.

Figura 6 – Construção do  $S_i$ . ([IEEE...](#), 2012)

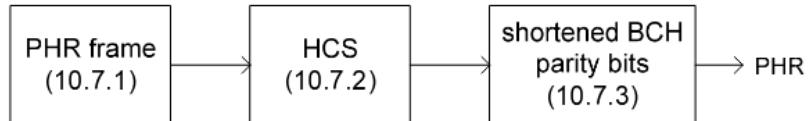

Figura 7 – Construção do PHR. ([IEEE...](#), 2012)

Por fim o SFD consiste no envio de um símbolo  $S_i$  invertido, ou seja, com os bits da sequência Kasami invertidos. Os zeros que são inseridos entre os elementos da sequência Kasami não são invertidos, permanecendo com o valor zero, e apenas a sequência tem seus bits invertidos.

### 2.2.2 PHR

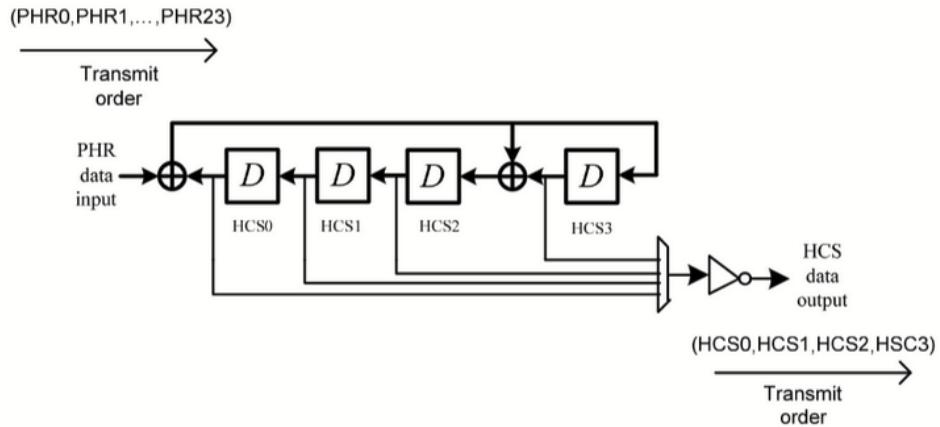

Para construir o PHR é necessário o PHR propriamente dito, mais o HCS (*Header Check Sequence*) e os bits de paridade do BCH.

O HCS é uma sequência de 4 bits de uma código de detecção de erros CRC-4 ITU. O CRC-4-ITH deve ser o complemento do resto da divisão em módulo-2 da informação do PHR pelo polinômio:

$$1 + x + x^4 \quad (2.3)$$

Esta operação pode ser implementada por um registrador de deslocamento, conforme arquitetura sugerida no documento da norma IEEE 802.15.6.

Após acrescentar os bits de CRC-4 ITU, 12 bits devem ser adicionados de um código BCH(40,28) encurtado.

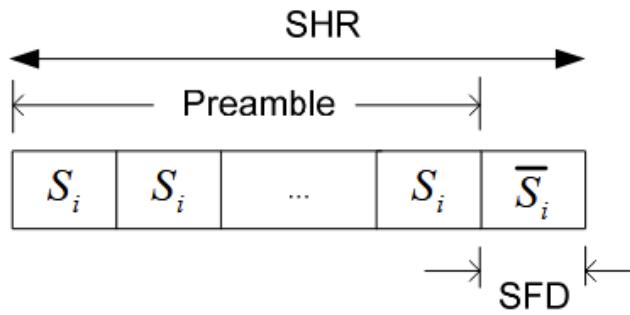

### 2.2.3 PSDU

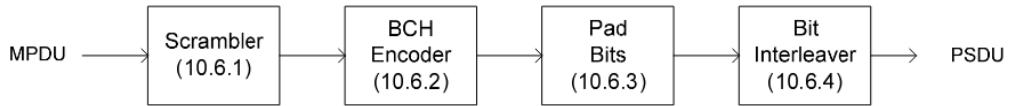

O PSDU é construído a partir do MPDU, que vem do MAC. O MPDU deve passar por um *scrambler*, um *encoder* BCH e um *interleaver*. A etapa "*Pad Bits*" é necessária apenas para algumas constelações específicas, para o caso deste projeto, essa etapa não será necessária.

Figura 8 – Construção do PSDU. ([IEEE..., 2012](#))

| Scrambler seed (SS) | Initialization vector<br>$x_{init} = x[-1] x[-2] \dots x[-14]$ |

|---------------------|----------------------------------------------------------------|

| 0                   | 0 0 1 0 1 1 1 0 0 1 1 0 1                                      |

| 1                   | 0 0 0 0 0 0 1 0 0 1 1 1 1                                      |

Figura 9 – Seleção da semente do scrambler. ([IEEE..., 2012](#))

O *scrambler* deve ser aplicado para eliminar longas sequências de 0s e 1s contidas no MPDU, de forma que o espectro de potência do sinal não tenha dependência nos dados reais.

O *scrambler* deve ser um *scrambler* aditivo, com um polinômio gerador dado pela equação:

$$x[n] = x[n - 2] \oplus x[n - 12] \oplus x[n - 13] \oplus x[n - 14] \quad (2.4)$$

Tipicamente esse tipo de *scrambler* é implementado por uma LFSR (*Linear Feedback Shift Register*).

Os bits do *scrambler* devem ser iniciados com uma semente. Essa semente é definida pela opção SS do PHR, e pode selecionar duas opções, conforme a figura 9.

O codificador BCH a ser implementado, deve ser o BCH( $n=63, k=51$ ) para o modo padrão. Para implementar este codificador deve-se utilizar o polinômio gerador:

$$g(x) = 1 + x^3 + x^4 + x^5 + x^8 + x^{10} + x^{12} \quad (2.5)$$

Sendo que os bits de paridade devem ser determinados calculando-se o resto do polinômio  $r(x)$ :

$$r(x) = \sum_{i=0}^{11} r_i x^i = x^{12} m(x) \mod g(x) \quad (2.6)$$

Onde  $m(x)$  é o polinômio da mensagem, que é definido da seguinte forma:

$$m(x) = \sum_{i=0}^{50} m_i x^i \quad (2.7)$$

Nas próximas seções, a teoria do BCH será discutida de maneira mais profunda.

Finalmente o *interleaver* deve ser aplicado antes da modulação para obter robustez contra a propagação de erros. O *interleaver* embaralha os bits da mensagem, mapeando blocos da mensagem em ordens diferentes. Isso deve ser feito conforme a equação:

$$\Pi(n) = nb_s \mod N_I \quad (2.8)$$

Onde  $N_I$  é o tamanho do *interleaver*,  $\Pi(n)$  é a nova posição para a qual o índice  $n$  deve ser permutado.

O tamanho do *interleaver* deve ser  $N_I = 192$ , e  $b_s = 37$ .

O *interleaver* é aplicado em blocos de tamanho 192, porém, no último bloco, se a quantidade de bits restante for menor que 192, então  $N_I$  deve ser determinado como a quantidade de bits restantes.

## 2.3 Corpos Finitos(Corpos de Galois)

Corpos finitos ou corpos de Galois é um conceito matemático que define um conjunto finito de números, em que se pode fazer operações dentro deste conjunto. Este conceito é utilizado em códigos de correção de erros, como os códigos Bose-Chaudhuri-Hocquenghem (BCH), o Reed-Solomon (RS) e o *low-density parity-check* (LDPC), além de ser utilizado em esquemas de criptografia como o *Advanced Encryption Standard* (AES). Operações em corpos finitos tem propriedades únicas que podem ser exploradas para simplificar estruturas de hardware, e pode tornar atrativo a implementação de sistemas utilizando corpos finitos.

Para entender o conceito de corpos finitos, algumas definições devem ser feitas.

### 2.3.1 Corpo

Um corpo, em álgebra abstrata, é um conjunto de elementos com 2 operações, a operação de adição e a operação de multiplicação, que são denotados pelos sinais  $+$  e  $\cdot$  respectivamente. Essas operações devem seguir as seguintes condições:

- Os elementos do conjunto devem formar um grupo comutativo em relação a  $+$  e deve ter um elemento identidade, que é chamado zero do corpo, e é denotado por 0.

- Os elementos do conjunto que não são iguais a zero, devem formar um grupo comutativo em relação a  $\cdot$  e deve ter um elemento identidade em relação a  $\cdot$  que é chamado de a identidade do corpo, e é denotado por 1.

- A operação de multiplicação é distributiva em relação a operação de adição:

$$a \cdot (b + c) = a \cdot b + a \cdot c \quad (2.9)$$

Um corpo finito então, é um corpo formado por um conjunto finito de elementos. O número de elementos em um corpo finito pode ser um número primo ou uma potência de um primo. Então para representar um corpo finito de  $p^q$  elementos, sendo  $p$  um número primo, escreve-se  $GF(p^q)$ . O número de elementos de um corpo também é chamado de ordem do corpo.

### 2.3.2 Ordem de um elemento

Dado um campo finito  $GF(p^q)$ , a ordem de um elemento  $\alpha \in GF(p^q)$  é o menor inteiro  $r$ , de tal modo que  $\alpha^r$  é igual ao elemento identidade do campo. A ordem de  $\alpha \in GF(p^q)$  sempre divide  $p^q - 1$ , deste modo  $\alpha^{p^q-1}$  é sempre igual ao elemento identidade.

### 2.3.3 Elemento primitivo

Definido a ordem de um elemento é possível definir um elemento primitivo. Este é definido como o elemento  $\alpha \in GF(p^q)$  que tem ordem igual a  $p^q - 1$

### 2.3.4 Polinômio Irredutível

Um polinômio irreduzível é uma polinômio que não pode ser fatorado em polinômios de graus menores.

Em campos finitos, um polinômio que tem coeficientes que são elementos de um campo  $GF(p^q)$  é dito ser um polinômio sobre  $GF(p^q)$ .

### 2.3.5 Polinômio Primitivo

Um polinômio irreduzível  $f(x)$  sobre  $GF(p^q)$  de grau  $q$  é dito ser um polinômio primitivo se o menor inteiro  $s$ , para o qual  $f(x)$  divide  $x^s - 1$ , for  $p^q - 1$ .

Todo elemento que é raiz de um polinômio primitivo de grau  $q$  sobre  $GF(p)$  é um elemento primitivo de  $GF(p^q)$ .

### 2.3.6 Polinômio Mínimo

Seja  $\alpha \in GF(p^q)$ . O polinômio mínimo de  $\alpha$  em relação a  $GF(p^q)$  é o polinômio de menor grau  $m(x)$  sobre  $GF(p^q)$  que satisfaz  $m(\alpha) = 0$ .

Polinômios mínimos são irreduzíveis.

Para cada elemento  $\alpha \in GF(p^q)$  existe um polinômio mínimo sobre  $GF(p)$  que tem o coeficiente de termo de maior grau do polinômio igual a identidade.

### 2.3.7 Base canônica

Uma base canônica de um campo finito  $GF(2^q)$  é definida como o conjunto  $\{1, \alpha, \alpha^2, \dots, \alpha^{q-1}\}$ , onde  $\alpha$  é a raiz de um polinômio irreduzível de grau  $q$  sobre  $GF(2)$ . Esta é chamada de uma base canônica de  $GF(2^q)$  sobre  $GF(2)$ .

Usando uma base canônica é possível representar um campo finito utilizando polinômios. Essa representação traz algumas vantagens quando se faz operações dentro de um corpo  $GF(2^q)$ . A soma, para um  $GF(2)$  é definida como um soma em módulo 2, que é equivalente a uma operação de XOR. Isso significa que a soma, utilizando uma representação em base canônica de um  $GF(2^q)$ , é equivalente a fazer uma operação XOR entre os coeficientes dos polinômios a serem somados.

Exemplo:  $\{1, \alpha, \alpha^2, \alpha^3\}$  é uma base canônica de  $GF(2^4)$ , sendo  $\alpha$  a raiz do polinômio primitivo  $x^4 + x + 1$ .

## 2.4 Aritmética em Corpos Finitos

A aritmética em corpos finitos pode ser feita de maneiras diferentes, a depender da representação utilizada para os corpos finitos. Além da representação usando base canônica, existem representações em potência, base normal, dual. Cada uma dessas representações fornece formas diferentes de se fazer aritmética. Neste trabalho, iremos focar em operações utilizando a base canônica, em corpos  $GF(2^q)$ .

### 2.4.1 Soma

A soma em corpos finitos, em particular para corpos do tipo  $GF(2^q)$ , pode ser feita utilizando uma operação XOR bit a bit. Considerando a representação em base canônica, é possível representar cada coeficiente do polinômio, como um bit, e fazer uma operação XOR em cada bit.

Por exemplo, considere  $\{1, \alpha, \alpha^2, \alpha^3\}$  uma base canônica de  $GF(2^4)$ , sendo  $\alpha$  a raiz do polinômio primitivo  $x^4 + x + 1$ . A soma de um elemento  $\alpha^2 + 1$  com um elemento  $\alpha^3 + \alpha^2 + \alpha$ , pode ser feita da forma:

$$(\alpha^2 + 1) + (\alpha^3 + \alpha^2 + \alpha) \Rightarrow 0101 + 1110 \quad (2.10)$$

$$\alpha^3 + (\alpha^2 \oplus \alpha^2) + \alpha + 1 \Rightarrow 0101 \oplus 1110 \quad (2.11)$$

$$\alpha^3 + \alpha + 1 \Rightarrow 1010 \quad (2.12)$$

### 2.4.2 Subtração

A subtração em um corpo  $GF(2^q)$  tem uma particularidade. Ela é exatamente igual a uma soma. Em outras palavras, para realizar uma subtração, basta realizar uma operação XOR bit a bit, exatamente como no caso da soma.

Por exemplo, realizando uma subtração com os elementos do exemplo do caso da soma resulta na mesma coisa que uma soma:

$$(\alpha^2 + 1) - (\alpha^3 + \alpha^2 + \alpha) \Rightarrow 0101 - 1110 \quad (2.13)$$

$$\alpha^3 + (\alpha^2 \oplus \alpha^2) + \alpha + 1 \Rightarrow 0101 \oplus 1110 \quad (2.14)$$

$$\alpha^3 + \alpha + 1 \Rightarrow 1010 \quad (2.15)$$

### 2.4.3 Multiplicação

A multiplicação para um corpo finito, utilizando um base canônica, é feita como uma multiplicação de polinômios com módulo com um polinômio irreduzível  $p(x)$ . Para entender o que isso quer dizer, podemos começar com um exemplo.

Considere um campo  $GF(2^6)$ , representado pela base canônica  $\{1, \alpha, \alpha^2, \alpha^3, \alpha^4, \alpha^5\}$ , sendo  $\alpha$  raiz do polinômio mínimo  $\alpha^6 + \alpha + 1$ . Considere também  $a = \alpha^5 + \alpha^4$ , e  $b = \alpha^1 + 1$ . A multiplicação  $a \cdot b$  será:

$$a \cdot b = (\alpha^5 + \alpha^4) \cdot (\alpha^1 + 1) \quad (2.16)$$

$$a \cdot b = \alpha^6 + (\alpha^5 + \alpha^5) + \alpha^4 = \alpha^6 + \alpha^4 \quad (2.17)$$

Para representar em base canônica, o maior grau de  $\alpha$  que pode-se usar neste exemplo é 5, deste modo é necessário simplificar  $\alpha^6$ . Para isso consideramos a definição do polinômio mínimo:

$$\alpha^6 + \alpha + 1 \quad (2.18)$$

De onde pode-se obter:

$$\alpha^6 = \alpha + 1 \quad (2.19)$$

Deste modo a resposta da multiplicação pode ser obtida como:

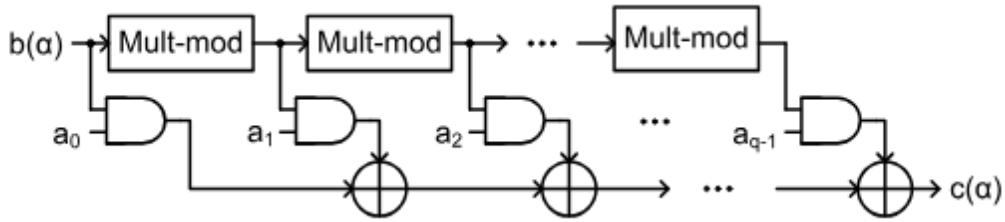

Figura 10 – Arquitetura de um multiplicador em base canônica. (ZHANG, 2016)

$$a \cdot b = \alpha^4 + \alpha + 1 \quad (2.20)$$

Esta é a forma analítica de se obter o resultado de uma multiplicação usando uma base canônica. O passo de reduzir  $\alpha^6$  para  $\alpha + 1$ , pode ser entendido como a forma analítica de realizar a operação de módulo com o polinômio mínimo.

A multiplicação em base canônica, pode ser definida também da seguinte forma:

Considere um corpo  $GF(2^q)$  com base canônica  $\{1, \alpha, \alpha^2, \dots, \alpha^{q-1}\}$ , construído com um polinômio irreduzível  $p(x)$  de grau  $q$ . Sejam  $a(\alpha) = a_0 + a_1\alpha + \dots + a_{q-1}\alpha^{q-1}$  e  $b(\alpha) = b_0 + b_1\alpha + \dots + b_{q-1}\alpha^{q-1}$  ( $a_i, b_i \in GF(2)$ ), dois elementos de  $GF(2^q)$ . O produto de  $a(\alpha)$  e  $b(\alpha)$  é:

$$c(\alpha) = a(\alpha)b(\alpha) \mod p(\alpha) \quad (2.21)$$

Essa operação pode ser reescrita como:

$$c(\alpha) = a_0b(\alpha) \mod p(\alpha) + a_1(b(\alpha)\alpha) \mod p(\alpha) + \dots + a_{q-1}(b(\alpha)\alpha^{q-1}) \mod p(\alpha) \quad (2.22)$$

Os termos  $b(\alpha)\alpha^i \mod p(\alpha)$  podem ser calculados de forma iterativa, como  $(b(\alpha)\alpha^{i-1} \mod p(\alpha))\alpha$ . Esse cálculo iterativo pode ser utilizado para criar uma estrutura em hardware capaz de fazer a multiplicação, como na imagem 10. Com um módulo "Mult-mod" que faz a operação  $b(\alpha) \cdot \alpha$ , é possível realizar a multiplicação. Para realizar um módulo desse tipo, é possível derivar uma arquitetura, de forma analítica, baseado no corpo finito em que se quer fazer a multiplicação. A seguir um exemplo desta arquitetura será explorado, que também é o módulo que será utilizado posteriormente nas arquiteturas propostas deste trabalho.

Exemplo: Considere um campo  $GF(2^6)$ , representado pela base canônica  $\{1, \alpha, \alpha^2, \alpha^3, \alpha^4, \alpha^5\}$ , sendo  $\alpha$  raiz do polinômio mínimo  $p(\alpha) = \alpha^6 + \alpha + 1$ . A multiplicação  $b(\alpha) \mod p()$  é:

$$b(\alpha)\alpha \mod p(\alpha) = (b_5\alpha^5 + b_4\alpha^4 + b_3\alpha^3 + b_2\alpha^2 + b_1\alpha + b_0)\alpha \quad (2.23)$$

$$b(\alpha)\alpha \mod p(\alpha) = b_5\alpha^6 + b_4\alpha^5 + b_3\alpha^4 + b_2\alpha^3 + b_1\alpha^2 + b_0\alpha \quad (2.24)$$

$$b(\alpha)\alpha \mod p(\alpha) = b_5(\alpha + 1) + b_4\alpha^5 + b_3\alpha^4 + b_2\alpha^3 + b_1\alpha^2 + b_0\alpha \quad (2.25)$$

$$b(\alpha)\alpha \mod p(\alpha) = b_4\alpha^5 + b_3\alpha^4 + b_2\alpha^3 + b_1\alpha^2 + (b_0 \oplus b_5)\alpha + b_5 \quad (2.26)$$

Deste modo pode-se implementar o "mult-mod" utilizando apenas uma porta XOR.

## 2.5 BCH

Códigos Bose-Chaudhuri-Hocquenghem (BCH) geralmente são usados em aplicações que tem erros aleatórios em bits, e precisam de codificadores de baixa complexidade. Exemplos de aplicação são comunicações óticas, transmissão de video digital (DVB) e memórias FLASH. Tais códigos se baseiam completamente nos conceitos de campos finitos, e usam estes conceitos como alicerce para a construção de um algoritmo de correção de erros.

Um código BCH( $n,k$ ) codifica uma mensagem de  $k$  bits em palavras de  $n$  bits. Para códigos construídos sobre  $GF(2^q)$ ,  $n$  pode ser máximo  $2^q - 1$ , sendo que quando  $n = 2^q - 1$ , o código é chamado de código primitivo.

Considere  $m(x)$ , a mensagem a ser transmitida, e  $c(x)$  a palavra codificada,  $c(x)$  então é definido como:

$$c(x) = m(x)g(x) \quad (2.27)$$

Sendo que  $g(x)$  é o polinômio gerador. O polinômio  $m(x)$ , é construído utilizando os bits da mensagem como coeficientes do polinômio, e o código gerado também tem como resultado os coeficientes de  $c(x)$ . A seguir será apresentado um exemplo para ilustrar.

Exemplo: Considere um código BCH(15, 7), construído sobre  $GF(2^4)$ , e o polinômio gerador  $g(x) = x^8 + x^7 + x^6 + x^4 + 1$ , e considere a mensagem  $m=0001011$ . Podemos representar  $m(x)$  como:

$$m(x) = x^3 + x + 1 \quad (2.28)$$

Deste modo, para calcular  $c(x)$ , se faz:

$$c(x) = (x^3 + x + 1) \cdot (x^8 + x^7 + x^6 + x^4 + 1) \quad (2.29)$$

$$c(x) = (x^1 + x^10 + x^9 + x^7 + x^3) + (x^9 + x^8 + x^7 + x^5 + x) + (x^8 + x^7 + x^6 + x^4 + 1) \quad (2.30)$$

$$c(x) = x^{11} + x^{10} + x^7 + x^6 + x^5 + x^3 + x + 1 \quad (2.31)$$

De modo que  $c(x)$  pode ser representado por 0000110011101011.

Uma forma alternativa de se realizar a codificação em BCH, é a codificação sistemática, e ela é realizada conforme a expressão:

$$c(x) = m(x)x^{n-k} + (m(x)x^{n-k})_{g(x)} \quad (2.32)$$

Sendo que  $(\cdot)_{g(x)}$  nesta expressão representa a operação de resto polinomial da divisão por  $g(x)$ . Essa operação funciona, como uma codificação BCH, porque, assim como na equação 2.27, nessa definição,  $c(x)$  é divisível por  $g(x)$ , e isso é suficiente para realizar a decodificação. A codificação sistemática é preferível, pois nesta, a mensagem original permanece intacta nos primeiros bits da palavra codificada, e apenas são acrescentados os bits do código em seguida a mensagem.

A ideia geral do BCH pode ser sintetizada da seguinte forma. O polinômio  $g(x)$  é construído de forma que ele tenha raízes consecutivas ( $\alpha, \alpha^2, \dots, \alpha^{(2t)}$ ). Isso significa que a mensagem codificada  $c(x)$ , também tem raízes nos mesmos elementos. Se a mensagem codificada  $c(x)$  tem algum de seus bits alterados, é possível verificar que, o resultado de  $c(\alpha^i)$  não igualaria a zero, mas traria um resultado diferente de zero. E a partir desses resultados, é possível aplicar algoritmos com os quais é possível identificar em qual bit ocorreu o erro, e assim corrigi-lo, quando a quantidade de erros é menor ou igual a  $t$ .

### 2.5.1 Decodificação BCH

A decodificação do BCH pode ser feita seguindo vários métodos diferentes. Pode-se citar os decodificadores do tipo *Hard-Decision*, os decodificadores do tipo *Chase BCH*, e os decodificadores do tipo *Interpolation-based Chase*. Os decodificadores do tipo *Hard-Decision* são os mais simples, e mais indicados para códigos BCH menores, com menor complexidade e é justamente essa categoria que focaremos neste trabalho.

Mesmo nos decodificadores *Hard-Decision*, existem diversas variações que podem ser exploradas, mas este tipo de decodificador segue uma estrutura com 3 passos: o cálculo de síndromes, *Key Equation Solver* (KES) e o *Chien Search*. A partir destes 3 passos é possível decodificar um código do tipo BCH.

### 2.5.2 Síndromes

Uma palavra  $c(x)$  é um código BCH, se e somente se ela tiver raiz nos mesmos elementos que são raiz de  $g(x)$ , que é o polinômio gerador. Deste modo, uma palavra recebida, pode ser representada por:

$$r(x) = c(x) + e(x) \quad (2.33)$$

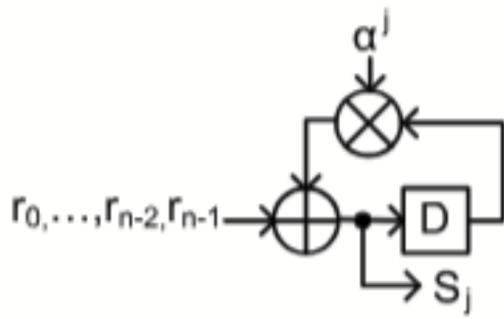

sendo  $c(x)$  o código original,  $e(x)$  o polinômio de erro e  $r(x)$  é o código recebido. Uma síndrome é definida como:

$$S_j(\alpha^j) = r(\alpha^j) = c(\alpha^j) + e(\alpha^j) = e(\alpha^j) = \sum_{i=0}^{n-1} e_i (\alpha^j)^i, 1 \leq j \leq 2t \quad (2.34)$$

Assumindo que  $r$  tem  $v$  erros nas posições  $i_1, i_2, \dots, i_v$ , e assumindo  $X_l = \alpha^{i_l}$  e considerando-se também que no caso do BCH,  $e_i$  pode assumir apenas os valores 0 e 1, pode-se escrever:

$$S_j = \sum_{l=1}^v (\alpha^j)^{i_l} = \sum_{l=1}^v X_l^j, 1 \leq j \leq 2t \quad (2.35)$$

Neste caso,  $X_l$  representa a localização dos erros, e portanto é chamado de localizador de erro.

A partir destas síndromes é possível chegar em um sistema de equações com  $2t$  equações e  $v$  variáveis.

$$\begin{aligned} S_1 &= X_1 + X_2 + \dots + X_v \\ S_2 &= X_1^2 + X_2^2 + \dots + X_v^2 \\ &\dots \\ S_{2t} &= X_1^{2t} + X_2^{2t} + \dots + X_v^{2t} \end{aligned} \quad (2.36)$$

Este sistema de equações torna possível a localização dos erros encontrados em  $r(x)$ . Para resolver este sistema, uma opção é utilizar o algoritmo de Peterson, que é detalhado na próxima seção

### 2.5.3 Algoritmo de Peterson

Peterson ([PETERSON, 1960](#)) demonstrou que o sistema de equações 2.36 pode ser resolvido de maneira mais fácil utilizando um polinômio localizador de erros na forma:

$$\Lambda(x) = \prod_{l=1}^v (1 - X_l x) = \Lambda_0 + \Lambda_1 x + \dots + \Lambda_v x^v \quad (2.37)$$

Neste caso pode-se relacionar as síndromes, com os coeficientes de  $\Lambda(x)$  com as equações:

$$\begin{aligned} S_1 + \Lambda_1 &= 0 \\ S_2 + \Lambda_1 S_1 + 2\Lambda_2 &= 0 \\ S_3 + \Lambda_1 S_2 + \Lambda_2 S_1 + 3\Lambda_3 &= 0 \\ \dots \\ S_v + \Lambda_1 S_{v-1} + \Lambda_2 S_{v-2} + \dots + \Lambda_{v-1} S_1 + v\Lambda_v &= 0 \\ S_{v+1} + \Lambda_1 S_v + \Lambda_2 S_{v-1} + \dots \Lambda_v S_1 &= 0 \\ \dots \\ S_{2t} + \Lambda_1 S_{2t-1} + \Lambda_2 S_{2t-2} + \dots + \Lambda_v S_{2t-v} &= 0 \end{aligned} \quad (2.38)$$

Sobre um corpo finito  $GF(2^q)$  pode-se escrever:

$$S_{2j} = \sum_{l=1}^v X_l^{2j} = (\sum_{l=1}^v X_l^j)^2 = S_j^2 \quad (2.39)$$

Com essa propriedade é possível obter que as equações pares, no sistema de equações 2.38, são redundantes as equações ímpares, de modo que é possível eliminá-las. Este sistema de equações pode ser representado em forma matricial:

$$A' \Lambda = \left[ \begin{array}{cccccc} 1 & 0 & 0 & \dots & 0 & 0 \\ S_2 & S_1 & 1 & \dots & 0 & 0 \\ S_4 & S_3 & S_2 & \dots & 0 & 0 \\ \vdots & \vdots & \vdots & \ddots & \vdots & \vdots \\ S_{2t-4} & S_{2t-5} & S_{2t-6} & \dots & S_{t-2} & S_{t-3} \\ S_{2t-2} & S_{2t-3} & S_{2t-4} & \dots & S_t & S_{t-1} \end{array} \right] \left[ \begin{array}{c} \Lambda_1 \\ \Lambda_2 \\ \Lambda_3 \\ \vdots \\ \Lambda_{t-1} \\ \Lambda_t \end{array} \right] = \left[ \begin{array}{c} S_1 \\ S_3 \\ S_5 \\ \vdots \\ S_{2t-3} \\ S_{2t-1} \end{array} \right] \quad (2.40)$$

Este sistema de equações tem uma solução única, se e somente se  $A'$  for inversível. Por causa da propriedade  $S_{2j} = S_j^2$ ,  $A'$  será inversível se houver  $t$  ou  $t-1$  erros. Se a matriz não for invertível, as 2 colunas mais à direita, e as 2 linhas mais abaixo são removidas, até se obter uma matriz invertível. Deste modo pode-se resolver o sistema de equações para se obter os coeficientes  $\Lambda_i$ .

Quando  $t$  é pequeno a matriz pode ser analiticamente e pode-se obter os resultados de forma direta. Por exemplo, os casos de  $t=1$  até  $t=3$  podem ser obtidos como:

Caso t=1:

$$\Lambda_1 = S_1 \quad (2.41)$$

Caso t=2:

$$\begin{aligned} \Lambda_1 &= S_1 \\ \Lambda_2 &= \frac{S_3 + S_1 S_2}{S_1} \end{aligned} \quad (2.42)$$

Caso t=3:

$$\begin{aligned} \Lambda_1 &= S_1 \\ \Lambda_2 &= \frac{S_1^2 + S_3 + S_5}{S_1^3 + S_3} \\ \Lambda_3 &= (S_1^3 + S_3) + S_1 \Lambda_2 \end{aligned} \quad (2.43)$$

Nestes caso não é necessário o processo iterativo para a solução do sistema de equação, o que pode fornecer uma otimização significativa da implementação em hardware.

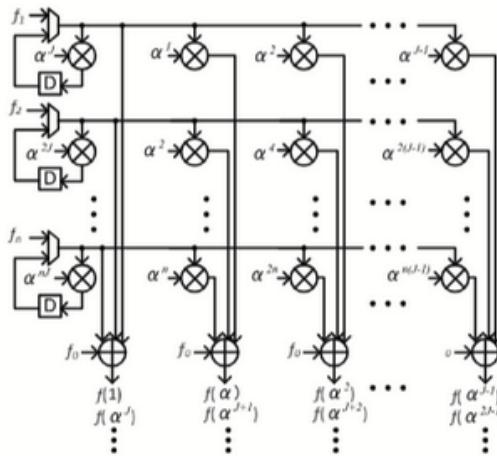

#### 2.5.4 Chien Search

Para resolver a equação 2.37 deve-se aplicar uma técnica para encontrar a raiz de uma equação em corpos finitos. Uma técnica que é bastante utilizada é o *Chien Search*, que consiste em buscar o resultado de forma exaustiva testando todos os resultados possíveis. Existem várias arquiteturas de *Chien Search* na literatura, sendo utilizadas buscas serialmente, em paralelo, ou parcialmente em paralelo, entre outras.

## 2.6 RISC-V

O RISC-V é uma ISA (*Instruction Set Architecture*) de código aberto que utiliza a licença BSD (*Berkeley Software Distribution*). Dizer que uma ISA é de código aberto com licença BSD significa dizer que o conjunto de instruções especificados por ela é livre para uso para qualquer fim sendo o código aberto ou fechado. Esta característica é um atrativo para esta ISA, pois permite o uso desta ISA para desenvolver processadores a nível de pesquisa e utilizar os compiladores e ferramentas já disponíveis para esta arquitetura.

O RISC-V foi inicialmente desenvolvido na Universidade da Califórnia, em Berkeley, com o início do projeto em 2010 (PATTERSON; HENNESSY, 2016). Ele se baseia em princípios RISC (*Reduced Instruction Set Computing*), que tem o objetivo de desenvolver

processadores com um conjunto reduzido de instruções. Este tipo é diferente de arquiteturas do tipo CISC(*Complex Instruction Set Computing*), que implementam operações mais complexas que podem ser chamadas em uma linha de código *Assembly* para realizar uma sequencia complexa de operações que podem demandar vários ciclos de *clock*. No caso de uma arquitetura RISC, a ideia é que as instruções possam ser executadas em 1 ciclo de *clock*, e então uma operação complexa pode ser executada utilizando várias linhas de *Assembly*. Esse tipo de abordagem tem a vantagem de poder se implementar arquiteturas mais simples e mais eficientes, por outro lado, arquiteturas CISC podem otimizar em tempo de execução, ao implementar operações complexas de forma otimizada.

Dessa forma a base do RISC-V é composta por um conjunto simples de operações. No entanto, uma peculiaridade da especificação do RISC-V, é que ele permite utilizar conjuntos diferentes de operações, a depender da necessidade do projetista. Para que isso seja possível, a especificação do RISC-V introduz o conceito de extensões. Cada extensão consiste em um conjunto de comandos que podem ser acrescentados em uma implementação de um processador RISC-V. As extensões base são extensões que contém as instruções mínimas para a implementação de um processador RISC-V. Estas extensões contém operações básicas de registro em memória e operações básicas com inteiros. As extensões base variam a depender do número de bits que se quer utilizar na arquitetura e o número de registradores. A especificação do RISC-V permite implementações de 32 bits, 64 bits e 128 bits. Além disso, há a opção de utilizar 32 registradores ou 16 registradores. Na tabela 1 as extensões base são apresentadas.

Tabela 1 – Exemplos de extensões base possíveis para uma implementação do *RISC-V*

| <b>Extensão Base</b> | <b>Descrição</b>                            |

|----------------------|---------------------------------------------|

| <b><i>RV32I</i></b>  | Módulo base de 32 bits e 32 registradores.  |

| <b><i>RV64I</i></b>  | Módulo base de 64 bits e 32 registradores.  |

| <b><i>RV128I</i></b> | Módulo base de 128 bits e 32 registradores. |

| <b><i>RV32E</i></b>  | Módulo base de 32 bits e 16 registradores.  |

| <b><i>RV64E</i></b>  | Módulo base de 64 bits e 16 registradores.  |

| <b><i>RV128E</i></b> | Módulo base de 128 bits e 16 registradores. |

A partir de alguma destas extensões base, podem ser acrescentadas operações, conforme a necessidade do projeto, como por exemplo, operações de multiplicação e divisão, operações com números flutuantes, e outros. Para fazer isso basta acrescentar extensões em cima de uma extensão base. Na tabela 2, algumas das extensões disponíveis na especificação são apresentadas.

Tabela 2 – Exemplos de extensões possíveis para uma implementação do RISC-V

| Extensão | Descrição                                                                                                                   |

|----------|-----------------------------------------------------------------------------------------------------------------------------|

| <b>M</b> | Extensão com instruções de multiplicação e divisão para inteiros.                                                           |

| <b>A</b> | Extensão que habilita instruções atômicas.                                                                                  |

| <b>C</b> | Extensão que habilita instruções comprimidas.                                                                               |

| <b>N</b> | Extensão com instruções para o uso de interrupções a nível de usuário.                                                      |

| <b>F</b> | Extensão com instruções para realizar operações com números flutuantes conforme padrão IEEE 754-200.                        |

| <b>D</b> | Extensão com instruções para realizar operações com números flutuantes de precisão dupla conforme padrão IEE 754-200.       |

| <b>Q</b> | Extensão com instruções para realizar operações com números flutuantes de precisão quádrupla conforme padrão IEEE 754-2008. |

A partir destas possibilidades, diversas implementações do RISC-V estão disponíveis em código aberto que podem ser utilizadas para a implementação deste projeto. Uma implementação particular disponível em código aberto sob a licença ISC, é o *PicoRV32*, do qual serão apresentados mais detalhes a seguir.

### 2.6.1 PicoRV32

O *PicoRV32* é um projeto em código aberto de um RISC-V. Esse projeto implementa um núcleo CPU que implementa a extensão RV32IMC do RISC-V. Isso significa que ele possui operações básicas com inteiros, multiplicação, divisão e possui suporte para instruções comprimidas. A opção de instruções comprimidas é interessante pois permite diminuir o tamanho do programa, fazendo com que se economize espaço de memória do programa.

Este CPU é customizável, permitindo que se implemente a CPU com as extensões RV32E, RV32I, RV32IC, RV32IM ou RV32IMC, além de possuir opções para a implementação de um controlador interno de interrupções. O código é implementado em *Verilog*, e as customizações da CPU podem ser realizadas por meio de macros disponíveis, que definem como o código em *Verilog* será compilado, adicionando ou não funcionalidades à CPU.

Outra opção de customização disponível é a utilização de interfaces de memória. Existe a opção de implementação de uma interface AXI4-Lite, uma interface *Wishbone* ou uma interface simplificada, própria do projeto, permitindo uma ampla compatibilidade com blocos externos.

### 2.6.2 PicoSoC

Também disponível no repositório do *PicoRV32* existe o *PicoSoC*. Este é uma implementação de um *PicoRV32*, com uma interface UART (*Universal Asynchronous Receiver/Transmitter*), uma implementação de SRAM e um controlador de memória QSPI (*Quad Serial Peripheral Interface*). Nesta implementação o programa é armazenado em uma memó-

Figura 11 – Blocos do *PicoRV32*, disponível em ([PICORV32...](#), 2025)

ria flash com interface QSPI, e pode ser acessado por meio do controlador. O bloco de UART permite comunicação de forma serial, podendo servir como interface para se comunicar com o processador. A memória SRAM é a memória que pode ser usada pelo programa em tempo de execução.

Esse SoC contém implementações para FPGAs de vários modelos diferentes, permitindo o uso dos recursos da FPGA, como memória flash e blocos de memória RAM, que podem ser acessíveis por meio de macros. Caso se deseje implementar este SoC em ASIC, deve-se utilizar IPs para implementar o bloco de SRAM, não podendo se utilizar o código como é descrito no repositório. Para este projeto, não será implementado o bloco de SRAM, sendo esta integração com IPs próprios, objeto de trabalhos futuros.

Na figura 11 um diagrama do *PicoSoC* é apresentado, no qual pode-se observar os blocos descritos. Além dos blocos descritos, existe a possibilidade de acrescentar mais blocos através de um barramento de 32 bits. Esse barramento segue o padrão de interface próprio do *PicoSoC* e não implementa padrões como o *Wishbone* ou o *AXI4-Lite*.

Para este trabalho, será utilizado o *PicoSoC* e a integração com o *PicoSoC* seguirá o padrão do diagrama apresentado na figura 11. Os blocos serão implementados em *Verilog* e serão integrados a partir do barramento de 32 bits apresentado no diagrama.

## 2.7 Estado da Arte

Um levantamento do estado da arte foi realizado para obter implementações de camadas físicas compatíveis com o padrão IEEE 802.15.6. A partir do levantamento foi

possível encontrar implementações em ASIC do padrão, assim como um implementação em FPGA. Também foram encontradas algumas implementações da comunicação UWB, mas em mais quantidade foram encontradas implementações da comunicação em NB, que são incluídas aqui, visto a semelhança na implementação da camada física. As implementações encontradas são datadas entre 2014 e 2017, isso acontece pois este período teve um maior esforço na pesquisa em torno deste assunto, visto que o padrão em questão foi publicado em 2012.

No artigo de (CHEN et al., 2013) um processador banda base para um transmissor WBAN é implementado. Neste caso, apenas o transmissor é implementado. Para este trabalho, foi implementado um transmissor NB, utilizando o padrão IEEE 802.15.6. A implementação para o processamento em banda base, segue os blocos descritos na norma, para o caso do NB, e se utiliza de uma FSM para controlar os blocos. Além disso, é utilizada a técnica de *clock gating*, para diminuir o consumo energético, garantindo que quando o sistema estiver ocioso, os blocos que não estão sendo usados, estejam desligados. Este sistema foi primeiro simulado em MATLAB, e depois implementado para ASIC, em tecnologia CMOS de 130 nm.

É importante notar que os requisitos do padrão para comunicação em NB, são bastante semelhantes ao UWB, no que tange ao processamento digital em banda base. Um ponto importante de distinção entre o NB e o UWB, é que no caso do NB é necessário um bloco a mais chamado de *spreader*. Esse bloco é responsável por repetir o bit que está chegando na entrada, dependendo da taxa de transmissão.

Uma outra implementação da norma para o caso de comunicação NB é (MATHEW et al., 2014) em que um transceptor banda base é implementado, utilizando o padrão IEEE 802.15.6. Para este caso, diferente do trabalho acima citado, o circuito é implementado utilizando FPGA. Uma particularidade dessa implementação é o decodificador BCH. Para realizar a etapa de KES, utiliza-se um algoritmo de Berlekamp Massey sem inversão, que é uma variante deste algoritmo que permite economizar energia na execução da operação. Antes da implementação em FPGA, foi simulado o sistema utilizando MATLAB, para validá-lo, e a partir disso o sistema foi implementado em FPGA, utilizando VHDL. Por fim, os resultados da execução foram monitorados utilizando um barramento PCIe, para monitorar o fluxo de dados, e o correto funcionamento do algoritmo.

O bloco BCH em particular é um dos blocos mais complexos do padrão, e ele permite uma variedade de abordagens na sua implementação, sendo assim um ponto chave de distinção entre os artigos.

No trabalho de (BACHMANN et al., 2014) uma abordagem mais versátil é apresentada com a implementação de um transceptor banda base multi padrão. O processador banda base digital deste artigo tem a capacidade de operar em 3 padrões diferentes, o IEEE 802.15.4 (ZigBee), IEEE 802.15.6 (WBAN) e o padrão *Bluetooth Smart (low energy, BLTE)*. Neste caso, o circuito é feito com blocos que sejam capazes de atender a cada um dos padrões. Um sistema

com vários *MUX*'s é utilizado, que alterna entre os blocos necessários para cada padrão. São implementados 2 BCHs nesse caso, um BCH(51, 63) e um BCH(31, 19), que são alternados dependendo do padrão. Além disso, blocos de *spreader*, *scrambler*, *interleaver* e *whitening* são alternados pelos *MUX*'s também. Este é um circuito que possui uma maior versatilidade, pois permite escolher entre diferentes padrões. Além disso são aplicadas técnicas para reduzir a energia consumida, como conversores DC-DC e uma unidade de gerenciamento de *clock*. O circuito foi implementado em tecnologia CMOS 40nm.

Ainda outra implementação de comunicação NB é apresentada em ([EL-MOHANDES; SHALABY; SAYED, 2018](#)), um transceptor banda base no padrão IEEE 802.15.6. Neste trabalho, o circuito foi implementado em ASIC. Para realizar isto, foi utilizado um fluxo de trabalho que inicia com simulações no MATLAB, e a partir destas, foram gerados IPs que foram simulados, testados em FPGA, e depois implementados em ASIC. A tecnologia usada neste trabalho é de 130nm. Outro ponto de distinção neste caso é a arquitetura do BCH, que utiliza uma arquitetura de Berlekamp-Massy e também utiliza um algoritmo de *Chien Search* sequencial que leva 63 ciclos para finalizar um operação.

Já em ([MANCHI; PAILY; GOGOI, 2017](#)) um transceptor UWB banda base compatível com o padrão IEEE 802.15.6 é implementado. Neste artigo é implementado um receptor e um transmissor, sendo implementada a porção digital da camada física descrita na norma. Este circuito é implementado tanto em tecnologia de 180nm, como também em tecnologia de 90nm. O circuito é validado em uma FPGA modelo ZYNQ, e utilizando simulação no MATLAB, para gerar sinais de entrada no circuito digital, e partir de um analisador lógico, obter os resultados. O circuito proposto, tem como diferencial uma arquitetura de BCH que contém uma arquitetura otimizada do KES, e uma arquitetura de *Chien Search* com terminação antecipada. Com essas modificações é possível economizar 42% em área e 38% em consumo de energia.

A partir dos resultados obtidos neste último trabalho, é possível intuir que uma implementação com arquiteturas mais simples para o BCH, pode levar a uma eficiência maior do circuito. Isso foi possível pela utilização do KES otimizado, em oposição a uma arquitetura como Berlekamp-Massy e também pela utilização de uma arquitetura otimizada do *Chien Search* com terminação antecipada. Com base nestas observações, uma arquitetura similar do KES será utilizada neste trabalho. Para o *Chien Search* será utilizada uma arquitetura com maior capacidade de paralelismo para obter maior desempenho, em oposição a ([EL-MOHANDES; SHALABY; SAYED, 2015](#)) que optou por uma arquitetura sequencial que demora 63 ciclos para realizar apenas este passo.

## 3 Aspectos Metodológicos

Circuitos Integrados de Aplicação Específica, ou ASIC (*Application Specific Integrated Circuit*) são circuitos desenvolvidos para um propósito específico utilizando uma tecnologia de fabricação de circuitos integrados. Exemplos de ASICs são microcontroladores, microprocessadores, chips controladores USB, memórias RAM, EEPROM entre outros. Esses tipos de circuitos são largamente utilizados na eletrônica. Isso se deve ao fato de que esses circuitos podem oferecer funções complexas, com alto desempenho e área reduzida, além de oferecer um custo menor por unidade, comparado ao mesmo circuito realizado utilizando componentes discretos.

Sistemas ASIC se diferenciam de FPGAs (*Field Programmable Gate Array*), pois FPGAs oferecem a possibilidade de utilizar uma matriz de portas lógicas e registradores interconectadas que podem ser reconfiguradas para realizar diversas funções, e assim é possível utilizar FPGAs para fazer a função de diversos circuitos diferentes, apenas rearranjando a matriz de células deste dispositivo. No caso do ASIC o circuito é desenvolvido e decidido antes da fabricação e não permite o rearranjo das suas conexões para trabalhar como um outro circuito.

Grande parte dos circuitos integrados são desenvolvidos em tecnologia CMOS (*Complementary Metal-Oxide-Semiconductor*). CMOS é uma tecnologia de fabricação que consiste na fabricação de transistores MOSFET (*Metal Oxide Semiconductor Field Effect Transistor*) do tipo NMOS e PMOS em um mesmo substrato de silício (RAZAVI, 2021). Essa tecnologia permitiu avanços no desenvolvimento de circuitos integrados como microprocessadores, e é largamente utilizada na indústria de semicondutores.

O uso desta tecnologia permitiu a implementação de circuitos cada vez mais eficientes, visto que com o passar do tempo é possível produzir transistores cada vez menores, o que leva a possibilidade fazer circuitos menores, que ocupam menos espaço, produzindo chips mais compactos. Outra vantagem é a tendência que há quando se reduz um transistor de este ficar mais rápido, isso acontece pois transistores menores tem menor capacidade nos seus terminais, que oferece um atraso menor, resultando em circuitos mais rápidos. Além disso o consumo de energia diminui com transistores menores. Isso permite o desenvolvimento de chips cada vez mais complexos e eficientes.

### 3.1 Níveis de Abstração

O grande desafio em projetos VLSI (*Very Large Scale Integration*) de circuitos integrados atuais é administrar a complexidade destes sistemas. Um SoC (*System on Chip*) moderno

---

conta com memórias, processadores, circuitos dedicados de como ADCs e interfaces IO de alta velocidade. Para produzir tais sistemas é necessário integrar centenas de milhões de transistores, ou bilhões de transistores. Para lidar com esta complexidade é necessário utilizar o conceito de níveis de abstração.

Para que seja possível desenvolver sistemas com tamanha complexidade é necessário dividir o projeto do sistema em diversos níveis de abstração, ocultando os detalhes sempre que eles não forem necessários. Projetos digitais em VLSI costumam ser particionados em 5 níveis de abstração: projeto de arquitetura, projeto de microarquitetura, projeto lógico, projeto de circuito e projeto físico. Esses níveis podem ser melhor explanados utilizando um exemplo, a arquitetura RISC-V especifica um conjunto de instruções, um modelo de registradores e memória. A partir desta arquitetura podem se especificar microarquiteturas que dividem a arquitetura em registradores e blocos funcionais. Exemplos de microarquiteturas de RISC-V que podem ser citados é a ESP32-C3, SiFive FE310 e GD32VF103. O projeto lógico define como que os blocos funcionais são estruturados, por exemplo pode se utilizar máquinas de estado que codificam seus estados utilizando uma codificação binária, em código Gray ou em codificação *One-Hot*. Descendo mais um nível de abstração, no projeto de circuito é descrito como que os transistores se interconectam para implementar a lógica. Nesse caso pode-se utilizar diferentes circuitos para implementar portas lógicas ou registradores, podendo-se inclusive projetar circuitos com o propósito de economizar energia, para projetos mais eficientes energeticamente. E finalmente o projeto físico lida com como esses transistores vão ser posicionados no substrato, e como que cada dispositivo irá se conectar fisicamente.

Outra prática importante para lidar com a complexidade é a prática do projeto estruturado. Esta prática usa os princípios de hierarquia, regularidade, modularidade e localidade. O princípio de hierarquia consiste em partitionar um projeto em várias hierarquias, onde hierarquias mais altas representam blocos mais complexos, e um grau de abstração maior, enquanto que hierarquias menores representam blocos menos complexos, até chegar no transistor que é o nível mais baixo de abstração. O uso de hierarquias torna mais fácil entender o circuito quando se analisa os componentes do circuito como caixas pretas com interfaces e funções bem definidas, ao invés de analisar cada transistor individualmente. Regularidade é o princípio de administrar a complexidade projetando o mínimo de blocos diferentes possível. Quando se cria blocos padronizados, é possível reutilizá-los, e desse modo é possível reduzir o trabalho, tornando o projeto mais eficiente. O princípio de modularidade refere-se ao uso de interfaces bem definidas para os blocos, de modo a evitar comportamentos inesperados. Finalmente o princípio de localidade refere-se a manter informação onde ela é usada, fisicamente e temporalmente.

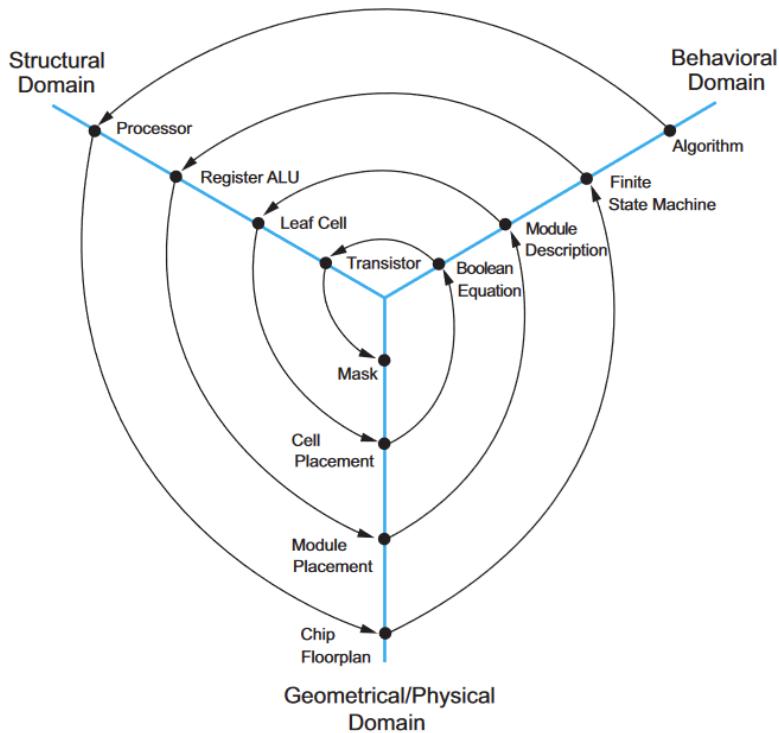

Outra forma de ver o particionamento de projeto que é conhecido na literatura é o diagrama Y. Esse diagrama divide o projeto de circuitos integrados digitais em 3 eixos, que representam 3 aspectos diferentes do projeto, esses são os 3 domínios: Estrutural, Compor-

Figura 12 – Diagrama Y de graus de abstração (WESTE; HARRIS, 2015)