# PhD THESIS

# Design, Optimization and Integration of Doherty Power Amplifier for 3G/4G Mobile Communications

Marcos Lajovic Carneiro

Electrical Engineering Department Brasília, 16/12/2013

**UNIVERSITY OF BRASÍLIA** FACULTY OF TECHNOLOGY

# UNIVERSITY OF BRASÍLIA FACULTY OF TECHNOLOGY ELECTRICAL ENGINEERING DEPARTMENT

# DESIGN, OPTIMIZATION AND INTEGRATION OF DOHERTY POWER AMPLIFIER FOR 3G/4G MOBILE COMMUNICATIONS

# MARCOS LAJOVIC CARNEIRO

# ADVISORS: PAULO HENRIQUE PORTELA DE CARVALHO ERIC KERHERVÉ CO-ADVISOR: NATHALIE DELTIMPLE

## PhD THESIS IN ELECTRICAL ENGINEERING

# PUBLICATION: PPGENE.TD 081/2013 BRASÍLIA/DF: DECEMBER – 2013

# UNIVERSITY OF BRASÍLIA FACULTY OF TECHNOLOGY ELECTRICAL ENGINEERING DEPARTMENT

# DESIGN, OPTIMIZATION AND INTEGRATION OF DOHERTY POWER AMPLIFIER FOR 3G/4G MOBILE COMMUNICATIONS

## MARCOS LAJOVIC CARNEIRO

THESIS SUBMITTED TO THE ELECTRICAL ENGINEERING DEPARTMENT FROM FACULTY OF TECHNOLOGY IN UNIVERSITY OF BRASILIA AS PART OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR IN ELECTRICAL ENGINEERING. APPROVED BY:

> José Camargo Costa, Docteur, UnB (President - Internal Examiner)

Paulo Henrique Portela de Carvalho, Docteur, UnB (Advisor)

Eric Kerhervé, Docteur, IPB ENSEIRB-MATMECA (Advisor)

Nathalie Deltimple, Docteur, IPB ENSEIRB-MATMECA (Co-Advisor)

Ricardo Augusto da Luz Reis, Doutor, UFRGS (External Examiner - Rapporteur)

Horácio Tertuliano Filho, Doutor, UFPR (External Examiner - Rapporteur)

BRASÍLIA/DF, 16 DECEMBER OF 2013

## FICHA CATALOGRÁFICA

| er Amplifier for 3G/4G Mobile |

|-------------------------------|

| x 297 mm (ENE/FT/UnB, Doutor, |

| e Tecnologia.                 |

|                               |

| 2.Efficiency enhancement      |

| 4.Optimization                |

| II. Título (série)            |

|                               |

## **REFERÊNCIA BIBLIOGRÁFICA**

CARNEIRO, M. L. (2013). Design, Optimization and Integration of Doherty Power Amplifier for 3G/4G Mobile Communications. Tese de Doutorado em Engenharia Elétrica, Publicação PPGENE.TD-081/2013, Departamento de Engenharia Elétrica, Universidade de Brasília, Brasília, DF, 142p.

## 1.1 CESSÃO DE DIREITOS

AUTOR: Marcos Lajovic Carneiro.

TÍTULO: Design, Optimization and Integration of Doherty Power Amplifier for 3G/4G Mobile Communications.

GRAU: Doutor ANO: 2013

É concedida à Universidade de Brasília permissão para reproduzir cópias desta tese de doutorado e para emprestar ou vender tais cópias somente para propósitos acadêmicos e científicos. O autor reserva outros direitos de publicação e nenhuma parte dessa tese de doutorado pode ser reproduzida sem autorização por escrito do autor.

Marcos Lajovic Carneiro

Rua 3, n°549, apto 503, Setor Oeste.

<sup>74.115-050</sup> Goiânia - GO - Brasil.

## ACKNOWLEDGMENT

The research team would like to thank STMicroelectronics and Didier Belot for the access on the CMOS 65nm technology and Magali de Matos for the chip measurements. We would like to thank the financial support of the CAPES/COFECUB program that allowed this international research cooperation between University of Brasília (Brazil) and University of Bordeaux 1 (France).

I would like to thank professors Paulo Portela, Eric Kerhervé and Nathalie Deltimple for the research orientation and the CAPES/COFECUB program. I would like to special thank Nathalie for my reception in Bordeaux and her kind treatment during hard times of this work.

I would like to thank the financial support of DPP/University of Brasília and Sérgio Granato de Araújo for the financial support for the participation on NEWCAS 2011 conference in Bordeaux. I would like to thank the financial support of IMS Laboratory for the chip production and for the participation in LASCAS 2013 conference in Peru.

I would like to thank my parents for the support in all steps of this journey. I would like to thank Priscilla Bonfim, Hugo Santos, Diogenes Reis, Leandro Assunção and Rodrigo Oliveira for the accommodation in Brasília. I would like to thank Melissa Pinheiro and Diogenes Reis (again) for the immense help in the study group in Brasília. I would like to thank Dean Karolak and Dwight Salas for the essential help on the chip design. Thanks for assistance in this work to Heider Marconi, Oskar Holstensson, Sophie Drean, Aurélien Larié, Adrien Tuffery and Massar.

Special thanks for the support during a long period of this work to Quéren dos Passos Freire. Thanks for the encouragement of the PhD in Brasília to Leonardo Brito, Sérgio Granato, Aline Oliveira. Thanks for making nice and unforgettable the PhD time in France to Maura, Marco, Juliana Calaça, Stephanie, Mouna, Aurélie Férault, Aurélie Rouillard, Hubert, Danièle Guillaume, Anne, Pauline, Mario, François Fadhuile, Youssef, Primoz Lajovic, Jose Lajovic.

#### RESUMO

# PROJETO, OTIMIZAÇÃO E INTEGRAÇÃO DE AMPLIFICADORES DE POTÊNCIA DOHERTY PARA COMUNICAÇÕES 3G/4G

Os sinais dos novos padrões de comunicação (LTE/LTE-Advanced) apresentam uma elevada diferença entre o pico e a média de sua potência (PAPR), sendo inadequados para o uso com os amplificadores de potência convencionais por apresentarem eficiência máxima apenas quando trabalham com sua potência máxima. Os novos sinais, na maior parte do tempo, demandam médias e baixas potências, concentrando a operação dos amplificadores de potência em uma região de baixa eficiência, o que provoca excessiva dissipação de energia em forma de calor e redução do tempo da bateria.

Os amplificadores de potência Doherty por apresentarem uma eficiência constante por uma larga faixa de potências representam uma solução favorável para o problema da PAPR. Devido à tendência atual de redução dos dispositivos e integração completa da cadeia de RF em um único *chip*, decidiu-se implementar esse amplificador de potência na tecnologia CMOS 65nm por ela já ser adequada à implementação de circuitos digitais, o que permite a integração de um sistema completo.

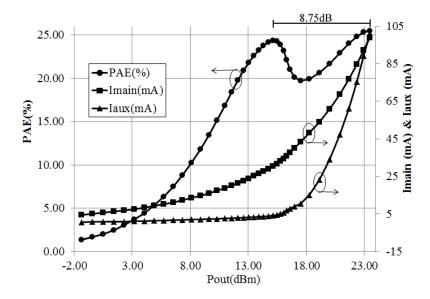

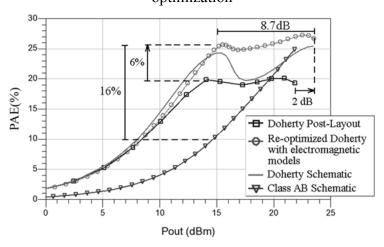

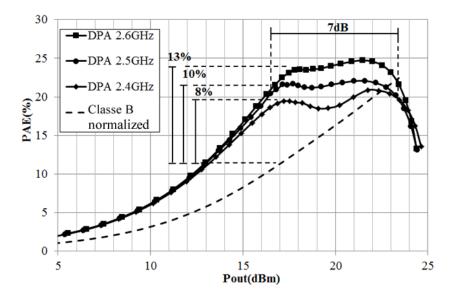

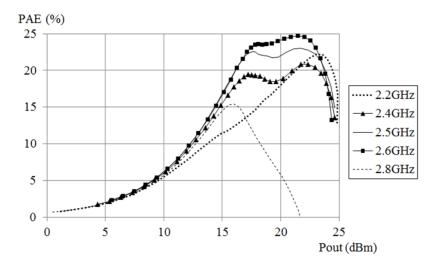

Este trabalho apresenta a metodologia de projeto e medições de um amplificador de potência Doherty totalmente integrado em tecnologia CMOS 65nm com desempenho de eficiência de potência adicionada (PAE) constante ao longo de uma retração de potência de 7dB. Medidas feitas de 2.4GHz à 2.6GHz mostram o desempenho constante de PAE começando no nível de 20% até 24%, com uma potência máxima de 23,4dBm. O circuito é totalmente descrito com todos os valores de componentes e detalhes de leiaute para posterior reprodução. As curvas que mostram o efeito de modulação ativa de carga, as correntes dos sub-amplificadores e o comportamento constante de PAE demonstram a implementação de um autêntico amplificador de potência Doherty. O circuito foi projetado com atenção especial para o baixo custo, utiliza apenas componentes discretos, cada sub-amplificador possui topologia cascode de saída simples e suas redes de entrada/saída são otimizadas para economizar área de *chip* e produzir um desempenho constante de PAE.

#### ABSTRACT

# DESIGN, OPTIMIZATION AND INTEGRATION OF DOHERTY POWER AMPLIFIERS FOR 3G/4G COMUNICATIONS

The signals of the new communication standards (LTE / LTE-Advanced) show a great difference between the peak and its average power (PAPR) being unsuitable for use with conventional power amplifiers because they present maximum efficiency only when working with maximum power. These signals demands low and medium power for most part of the time, which concentrates the operation of power amplifiers in a region of low efficiency, resulting in excessive heat dissipation and reduction of battery time.

Doherty power amplifiers for presenting a constant efficiency for a wide power range represent a favorable solution to this problem. Given the current trend of reducing devices and full integration of RF chain on a single chip, it was decided to implement this power amplifier in 65nm CMOS technology due to its performance for digital circuits, allowing the integration of a whole system.

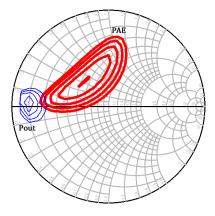

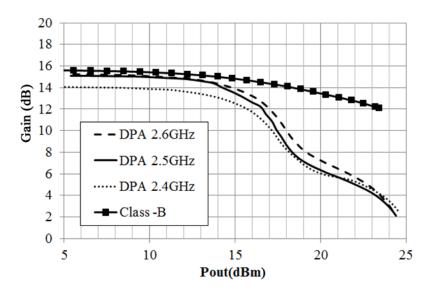

This work presents the design methodology and measurements results of a fully integrated Doherty Power Amplifier in 65 nm CMOS technology with constant PAE over a 7 dB backoff. Measurements from 2.4 GHz to 2.6 GHz show constant PAE performance starting in 20% level up to 24% with a maximum output power of 23.4 dBm. The circuit is fully described with all components values and layout details for further reproduction. Curves showing the active load-pull effect, sub-amplifiers behavior and constant PAE prove that it is a genuine Doherty Power Amplifier. The circuit was designed with special attention to low cost, it is composed by only lumped components, each sub-amplifier has single-ended cascode topology and their input/output networks are optimized to save die area and to produce a constant PAE.

## RESUMÉ

#### CONCEPTION, OPTIMISATION ET INTÉGRATION D'AMPLIFICATEURS DE PUISSASNCE DOHERTY POUR DES COMUNICATIONS 3G/4G

L'amplificateur de puissance (PA) est l'élément qui consomme le plus d'énergie dans les architectures d'émission-réception RF des terminaux mobiles. Les PAs conventionnels ont un rendement maximum seulement au niveau de puissance maximum, tandis que pour des niveaux de puissance plus bas, le rendement des PAs est très faible. Or les nouveaux standards de communications à haut débit (4G/LTE advanced) utilisent des modulations à enveloppe non-constante. Ainsi, le rapport entre la puissance maximum et la puissance moyenne du signal (PAPR – Peak to Average Power Ratio) est élevé. C'est le cas également pour l'OFDM qui possède un fort PAPR avec les porteuses multiples. Ainsi, lorsqu'un signal a un fort PAPR, cela signifie que le rendement moyen du PA utilisé est faible. La conséquence directe est la rapide décharge des batteries des terminaux mobiles.

L'Amplificateur de Puissance Doherty (APD) est une technique connue d'amélioration du rendement. Cette technique permet d'augmenter le rendement moyen des amplificateurs en améliorant le rendement aux faibles niveaux de puissance, tout en maintenant le rendement maximum sur une plus grande plage de puissance de sortie. Cette technique est bien adaptée pour résoudre le problème de rendement pour les signaux à forts PAPR. De nombreux travaux proposent des solutions intégrées des APD dans une technologie à faible coût, mais au détriment du maintien d'un rendement à puissance ajoutée (Power Added-Efficiency, PAE) constant sur une grande plage de puissance.

Nos travaux de recherche proposent un APD totalement intégré en technologie 65nm CMOS de STMicroelectronics à 2,535 GHz avec une PAE constante sur une plage de recul en puissance de sortie de 8 dB. Pour la conception de cet amplificateur, nous avons utilisé sept niveaux de métaux sur les dix couches de métaux de la technologie, les capacités sont de type MOM afin de respecter des contraintes faible coût.

Le principe de l'APD est d'utiliser l'effet connu sous le nom de « load-pull actif » : une charge vue par une source de courant peut être modifiée par l'application d'un courant provenant d'une deuxième source. Pour atteindre cet objectif, l'architecture Doherty utilise

deux amplificateurs de classes différentes en parallèle. Le PA principal (classiquement polarisé en classe B ou AB) fonctionne pour tous les niveaux de puissance et le PA auxiliaire (classiquement en classe C) ne fonctionne que pour les niveaux de puissance moyens et forts. L'augmentation de rendement s'explique par la transformation d'impédance de drain du PA principal, à cause de la combinaison de deux facteurs en même temps, la charge inversée vue par la ligne de transmission d'un quart d'onde et le courant du PA auxiliaire qui augmente. En effet, lorsque le courant du PA auxiliaire augmente, l'impédance vue par le PA principal se réduit.

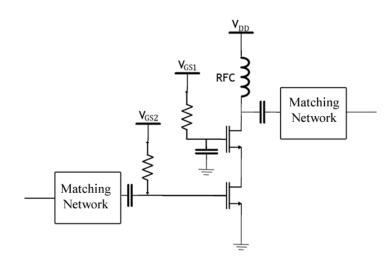

L'APD a été conçu avec les transistors à drain étendu haute tension pour soutenir une grande excursion de tension et produire des niveaux de puissance de sortie plus élevés. Les limites de Vdd et Vgs du transistor sont de 2.75V et de 5.5V, respectivement. Chaque sous-amplificateur a été conçu avec une topologie cascode pour donner au PA une meilleure isolation vis-à-vis des effets de désadaptation d'impédances entre la sortie et l'entrée. De plus, cette topologie permet d'avoir une plus grande tension d'alimentation Vdd par rapport à la topologie source commune.

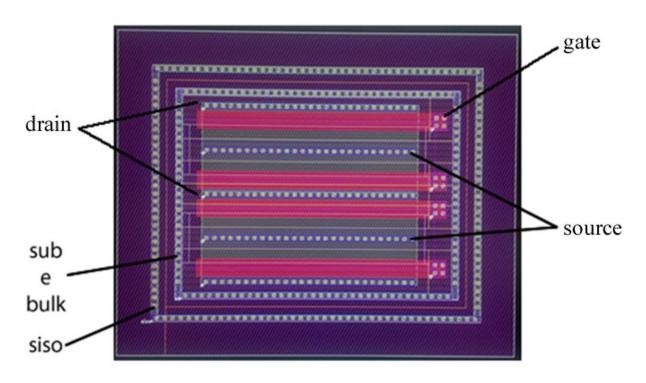

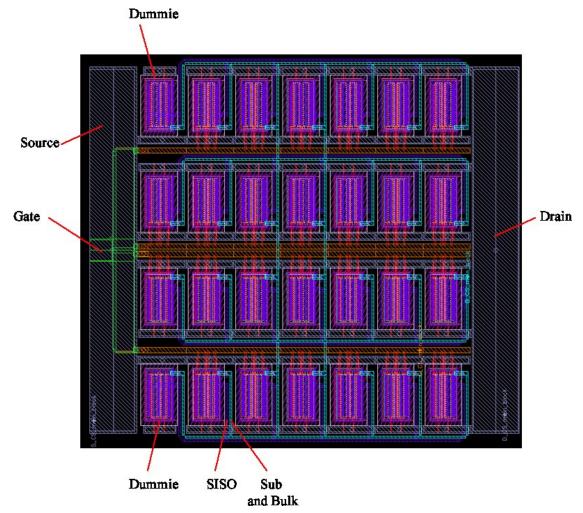

Les deux amplificateurs, principal et auxiliaire, ne sont cependant pas identiques. En effet, les dimensions des transistors dépendent du courant traversant chaque amplificateur. Ainsi, le transistor grille commune du PA principal est constitué de 28 transistors en parallèle, tandis que le transistor source commune du PA principal est composé de 26 transistors en parallèle. Pour le PA auxiliaire, le transistor grille commune est composé de 26 transistors en parallèle et son transistor source commune est composé de 14 transistors en parallèle.

Chaque sous-amplificateur a été conçu et optimisé individuellement en prenant en compte les réseaux d'adaptation, l'inductance d'arrêt, les impédances d'entrée prévues par le diviseur de puissance et l'impédance de sortie prévue pour avoir l'effet loadpull actif de l'APD. Tout au long du travail de conception, les performances des deux PAs ont été tracées sur le même graphique pour équilibrer correctement le point de compression de chacun. Les courbes de PAE de chacun ont été optimisées dans le but de produire un APD avec une PAE constante sur une large gamme de puissance.

Après la connexion des sous-amplificateurs dans le même schéma électrique, les lignes de transmission à éléments localisés ont été ajoutées, puis la topologie a été ré-optimisée pour

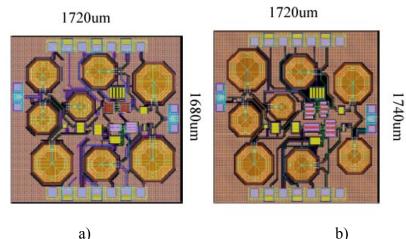

réduire le nombre d'inductances et ainsi réduire l'espace utilisé dans la puce. À l'entrée, le diviseur de Wilkinson, la ligne de transmission déphasage et les réseaux d'adaptation d'entrée des PAs principal et auxiliaire ont été fusionnés et optimisés. À la sortie de l'APD, les réseaux d'adaptation de sortie des deux PAs et la ligne de transmission d'inversion de charge ont aussi été fusionnés et optimisés. Pour atteindre l'objectif d'avoir une PAE constante, une méthodologie d'optimisation séquentielle a été appliquée pour bien équilibrer tous les éléments dans le schéma de l'APD en respectant toutes les limites de tensions des transistors. Le circuit a été implémenté dans une surface de 1,72x1,68mm<sup>2</sup>. Il a été conçu pour être mesuré avec des sondes directement positionnées sur les trois différents types de plots.

Ce travail présente la méthodologie de conception et des résultats de mesure d'un amplificateur de puissance Doherty entièrement intégré dans la technologie 65 nm CMOS avec une PAE constante sur 7 dB de plage de puissance. Les mesures de 2,4 GHz à 2,6 GHz montrent des performances constantes en PAE de 20% jusqu'à 24% avec une puissance de sortie maximale de 23,4 dBm. Le circuit est entièrement décrit avec les valeurs des composants et les détails de layout pour permettre sa reproduction. Ce travail montre l'effet de modulation active de charge, le comportement en courant des sous-amplificateurs et la performance constante en PAE, ce qui démontre l'implémentation d'un véritable amplificateur de puissance Doherty. Le circuit est composé uniquement d'éléments localisés, et les réseaux d'entrée et de sortie sont optimisés pour réduire la taille de la puce et pour produire une PAE constante.

L'amplificateur de puissance Doherty présenté est le premier APD totalement intégré en technologie 65 nm CMOS avec une PAE constante sur une large gamme de puissance. Il respecte de ce point de vue la théorie de Doherty. La comparaison avec un amplificateur de puissance classique polarisé en classe AB montre une amélioration de la PAE pour les niveaux de faible et moyenne puissance, permettant ainsi d'augmenter nettement le rendement moyen de l'amplificateur. Aucun autre APD publié ne présentait ce type de caractéristique en rendement dans cette technologie. La technologie 65nm CMOS est généralement plus appropriée pour les applications numériques, par conséquent, l'utilisation de cette technologie s'inscrit dans la tendance actuelle du développement d'un système complet sur une seule puce, où les étages numérique et analogique sont intégrés sur la même puce silicium.

### SUMMARY

| 1  | I     | NTRODUCTION 2                                                     |

|----|-------|-------------------------------------------------------------------|

|    | 1.1   | MOTIVATION2                                                       |

|    | 1.2   | PROPOSED SOLUTION                                                 |

|    | 1.3   | STATE-OF-THE-ART                                                  |

|    | 1.4   | THESIS ORGANIZATION7                                              |

|    | 1.5   | LIST OF PUBLISHED PAPERS OF THIS RESEACH7                         |

| 2  | ı     | FOURTH GENERATION MOBILE COMMUNICATIONS AND CMOS                  |

|    |       | NOLOGY 9                                                          |

| 1. | 2.1   | INTRODUCTION                                                      |

|    | 2.1   | MOBILE COMMUNICATIONS EVOLUTION                                   |

|    | 2.2   |                                                                   |

|    | 2.2.1 |                                                                   |

|    |       |                                                                   |

|    | 2.3   | THE CMOS TECHNOLOGY    16      CONCLUSIONS    17                  |

|    | 2.4   | CONCLUSIONS                                                       |

| 3  | 1     | POWER AMPLIFIERS BIBLIOGRAPHIC REVIEW 18                          |

|    | 3.1   | INTRODUCTION                                                      |

|    | 3.2   | MEASUREMENTS OF POWER, GAIN AND EFFICIENCY IN A PA                |

|    | 3.3   | LINEARITY MEASUREMENTS20                                          |

|    | 3.4   | PAPR PROBLEM ANALYSIS ON THE PA23                                 |

|    | 3.5   | POWER AMPLIFIER CELLS                                             |

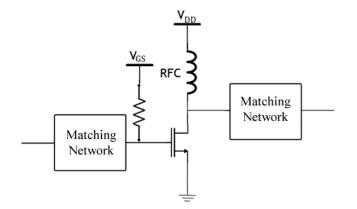

|    | 3.5.1 | Common-Source Topology and Integrated Choke Inductances Details25 |

|    | 3.5.2 |                                                                   |

|    | 3.5.3 | Differential Topology                                             |

|    | 3.6   | POWER AMPLIFIER CLASSES                                           |

|    | 3.6.1 | Sinusoidal classes A, B, AB and C28                               |

|    | 3.6.2 |                                                                   |

|    | 3.7   | IMPEDANCE MATCHING: LOAD-PULL/SOURCE-PULL METHOD                  |

|    | 3.8   | CONVENTIONAL DESIGN METHODOLOGY FOR INTEGRATED                    |

|    |       | VER AMPLIFIERS                                                    |

|    | 100   | / LAX / XIVII LAT IL/IXO                                          |

| <b>3.9 EFFICIENCY ENHACEMENT TECHNIQUES</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 3.9.1 Dynamic Polarization Technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 40                                                                                                                |

| <b>3.9.2</b> Envelope Elimination and Restoration Technique (EE&R)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 41                                                                                                                |

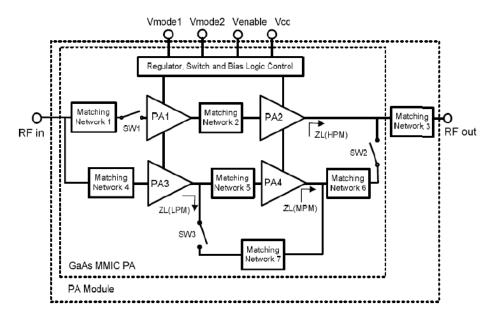

| 3.9.3 Power Cell Switching Technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 42                                                                                                                |

| 3.9.4 Envelope Tracking Technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42                                                                                                                |

| 3.9.5 Bypass Stage Technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 43                                                                                                                |

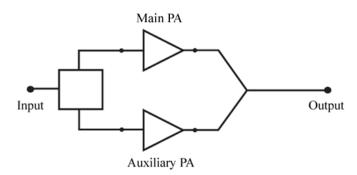

| 3.9.6 Doherty Technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 44                                                                                                                |

| 3.10 DOHERTY POWER AMPLIFIER THEORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 45                                                                                                                |

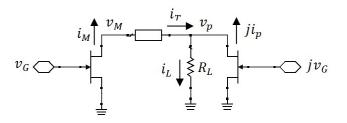

| 3.10.1 Doherty Power Amplifier Load Modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 46                                                                                                                |

| 3.10.2 Sub-PAs Output Currents Equations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50                                                                                                                |

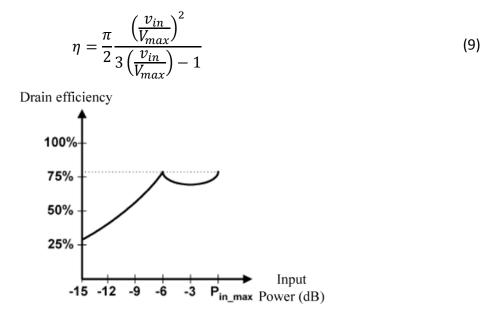

| 3.10.3 Design Equations and Doherty Power Amplifier Performan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ice53                                                                                                             |

| 3.11 DOHERTY POWER AMPLIFIER STATE OF THE ART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 56                                                                                                                |

| 3.12 CONCLUSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 60                                                                                                                |

| 4 DOHERTY POWER AMPLIFIER DESIGN METHODOLO<br>DESCRIPTION AND SIMULATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | )GY, CIRCUIT<br>61                                                                                                |

| 4.1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 61                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                   |

| 4.2 CONVENTIONAL DOHERTY POWER AMPLIFI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ER DESIGN                                                                                                         |

| 4.2 CONVENTIONAL DOHERTY POWER AMPLIFI<br>METHODOLOGY ANALYSIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 61                                                                                                                |

| METHODOLOGY ANALYSIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 61<br>OGY AND SUB                                                                                                 |

| METHODOLOGY ANALYSIS<br>4.3 STUDY ON THE DOHERTY POWER AMPLIFIER TOPOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 61<br>OGY AND SUB<br>63                                                                                           |

| METHODOLOGY ANALYSIS<br>4.3 STUDY ON THE DOHERTY POWER AMPLIFIER TOPOL<br>AMPLIFIERS CLASSES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 61<br>OGY AND SUB<br>63<br>HE DOHERTY                                                                             |

| METHODOLOGY ANALYSIS<br>4.3 STUDY ON THE DOHERTY POWER AMPLIFIER TOPOL<br>AMPLIFIERS CLASSES<br>4.4 NEW DESIGN METHODOLOGY PROPOSAL FOR TH                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 61<br>OGY AND SUB<br>63<br>HE DOHERTY<br>65                                                                       |

| METHODOLOGY ANALYSIS<br>4.3 STUDY ON THE DOHERTY POWER AMPLIFIER TOPOL<br>AMPLIFIERS CLASSES<br>4.4 NEW DESIGN METHODOLOGY PROPOSAL FOR TH<br>POWER AMPLIFIER                                                                                                                                                                                                                                                                                                                                                                                                                                           | 61<br>OGY AND SUB<br>63<br>HE DOHERTY<br>65<br>65                                                                 |

| METHODOLOGY ANALYSIS<br>4.3 STUDY ON THE DOHERTY POWER AMPLIFIER TOPOL<br>AMPLIFIERS CLASSES<br>4.4 NEW DESIGN METHODOLOGY PROPOSAL FOR TH<br>POWER AMPLIFIER<br>4.4.1 Impedance Analysis on the Doherty Power Amplifier                                                                                                                                                                                                                                                                                                                                                                                | 61<br>OGY AND SUB<br>63<br>HE DOHERTY<br>65<br>66                                                                 |

| METHODOLOGY ANALYSIS<br>4.3 STUDY ON THE DOHERTY POWER AMPLIFIER TOPOL<br>AMPLIFIERS CLASSES<br>4.4 NEW DESIGN METHODOLOGY PROPOSAL FOR TH<br>POWER AMPLIFIER<br>4.4.1 Impedance Analysis on the Doherty Power Amplifier<br>4.4.2 Sub-PAs Design                                                                                                                                                                                                                                                                                                                                                        | 61<br>OGY AND SUB<br>63<br>HE DOHERTY<br>65<br>65<br>66<br>67<br>76                                               |

| METHODOLOGY ANALYSIS<br>4.3 STUDY ON THE DOHERTY POWER AMPLIFIER TOPOL<br>AMPLIFIERS CLASSES<br>4.4 NEW DESIGN METHODOLOGY PROPOSAL FOR TH<br>POWER AMPLIFIER<br>4.4.1 Impedance Analysis on the Doherty Power Amplifier<br>4.4.2 Sub-PAs Design<br>4.4.3 Final Individual Design Stage of the Sub-PAs                                                                                                                                                                                                                                                                                                  | 61<br>OGY AND SUB<br>63<br>HE DOHERTY<br>65<br>66<br>67<br>76                                                     |

| METHODOLOGY ANALYSIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 61<br>OGY AND SUB<br>63<br>HE DOHERTY<br>65<br>66<br>67<br>76<br>78<br>79                                         |

| METHODOLOGY ANALYSIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 61<br>OGY AND SUB<br>63<br>HE DOHERTY<br>65<br>66<br>67<br>76<br>78<br>79<br>                                     |

| METHODOLOGY ANALYSIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 61<br>OGY AND SUB<br>63<br>HE DOHERTY<br>65<br>66<br>67<br>76<br>78<br>79<br>79<br>                               |

| <ul> <li>METHODOLOGY ANALYSIS</li> <li>4.3 STUDY ON THE DOHERTY POWER AMPLIFIER TOPOL<br/>AMPLIFIERS CLASSES</li> <li>4.4 NEW DESIGN METHODOLOGY PROPOSAL FOR TH<br/>POWER AMPLIFIER</li> <li>4.4.1 Impedance Analysis on the Doherty Power Amplifier</li> <li>4.4.2 Sub-PAs Design</li> <li>4.4.3 Final Individual Design Stage of the Sub-PAs</li> <li>4.4.4 Power Splitter Design</li> <li>4.4.5 Transmission Lines Design and Optimization</li> <li>4.4.6 Layout Pre-Analysis</li> <li>4.4.7 Input and Output Network Matching Optimization for Chip</li> </ul>                                     | 61<br>OGY AND SUB<br>63<br>HE DOHERTY<br>65<br>66<br>67<br>76<br>78<br>79<br>79<br>85<br>Area Reduction<br>       |

| <ul> <li>METHODOLOGY ANALYSIS</li> <li>4.3 STUDY ON THE DOHERTY POWER AMPLIFIER TOPOL<br/>AMPLIFIERS CLASSES</li> <li>4.4 NEW DESIGN METHODOLOGY PROPOSAL FOR TH<br/>POWER AMPLIFIER</li> <li>4.4.1 Impedance Analysis on the Doherty Power Amplifier</li> <li>4.4.2 Sub-PAs Design</li> <li>4.4.3 Final Individual Design Stage of the Sub-PAs</li> <li>4.4.4 Power Splitter Design</li> <li>4.4.5 Transmission Lines Design and Optimization</li> <li>4.4.6 Layout Pre-Analysis</li> <li>4.4.7 Input and Output Network Matching Optimization for Chip<br/>and the Final Schematic Details</li> </ul> | 61<br>OGY AND SUB<br>63<br>HE DOHERTY<br>65<br>66<br>67<br>76<br>78<br>79<br>79<br>85<br>Area Reduction<br>86<br> |

|    | 4.4. | 11 Design Variables Summary                      |          |

|----|------|--------------------------------------------------|----------|

|    | 4.5  | LTE SIGNAL TRANSMISSION                          |          |

|    | 4.6  | CONCLUSIONS                                      | 108      |

| 5  |      | MEASUREMENTS AND RESULTS ANALYSIS                | 109      |

|    | 5.1  | INTRODUCTION                                     | 109      |

|    | 5.2  | THE CHIP AND MEASUREMENTS SETUP                  | 109      |

|    | 5.3  | MEASUREMENT RESULTS                              | 112      |

|    | 5.4  | RESULTS ANALYSIS AND COMPARISONS                 | 116      |

|    | 5.5  | SUMMARY OF CHIP PERFORMANCE AND SPECIFICATIONS   | 120      |

|    | 5.6  | COMPARISON WITH STATE-OF-ART                     | 121      |

|    | 5.7  | CONCLUSIONS                                      | 123      |

| 6  |      | FINAL CONCLUSIONS AND PROPOSALS FOR FUTURE WORKS | 124      |

| R  | EFE  | RENCES                                           | 132      |

| A  | NNE  | X A – 65NM CMOS STMICROELECTRONICS DESIG KIT COM | IPONENTS |

| SI | ETUI | P FOR THE ADVANCED DESIGN SYSTEM 2009            | 134      |

| A  | NNE  | X B - CMOS RESTRICTIONS                          | 140      |

## TABLES LIST

| Table 1.1 – PAPR for 3G/4G Standards                                            | 3           |

|---------------------------------------------------------------------------------|-------------|

| Table 1.2 – LTE specifications                                                  | 4           |

| Table 1.3 – Design specifications, objectives and restrictions                  | 5           |

| Table 1.4 - CMP prices in 2012 for integrated circuits prototypes designed with | ı standard  |

| options [20]                                                                    | 5           |

| Table 1.5 – Comparing the State-of-The-Art of Fully Integrated Doherty Power Am | plifiers in |

| CMOS Technology (measurements results)                                          | 6           |

| Table 2.1 – Characteristics of main wireless communication standard systems [6] | 13          |

| Table 3.1 – PA sinusoidal classes summary                                       |             |

| Table 3.2 – Class E and F summary.                                              |             |

| Table 3.3 – Description of the parameters from the circuit in Figure 3.39       | 46          |

| Table 3.4 – Parameters of the simplified DPA of the Figure 3.46                 | 51          |

| Table 3.5 – Design Equations of the Doherty Power Amplifier                     | 54          |

| Table 3.6 – Load power, DC power and drain efficiency on the low power region   | 55          |

| Table 3.7 – Load power, DC power and drain efficiency on the high power region  | 55          |

| Table 3.8 – Previous work on the Doherty Power Amplifier                        |             |

| Table 4.1 – DPA Topologies                                                      | 64          |

| Table 4.2 – Optimization variables on the sub-PAs                               | 68          |

| Table 4.3 – Fixed and adjustable variables on the sub-PAs                       | 69          |

| Table 4.4 – Sub-PAs restrictions and objectives                                 | 74          |

| Table 4.5 – Resistors                                                           |             |

| Table 4.6 – Capacitors                                                          |             |

| Table 4.7 – Inductors                                                           |             |

| Table 4.8 – Transistors                                                         |             |

| Table 4.9 - Polarization                                                        | 90          |

| Figure 4.34 - Monte Carlo simulations for performance variationTable 4.10 -     | Main PA     |

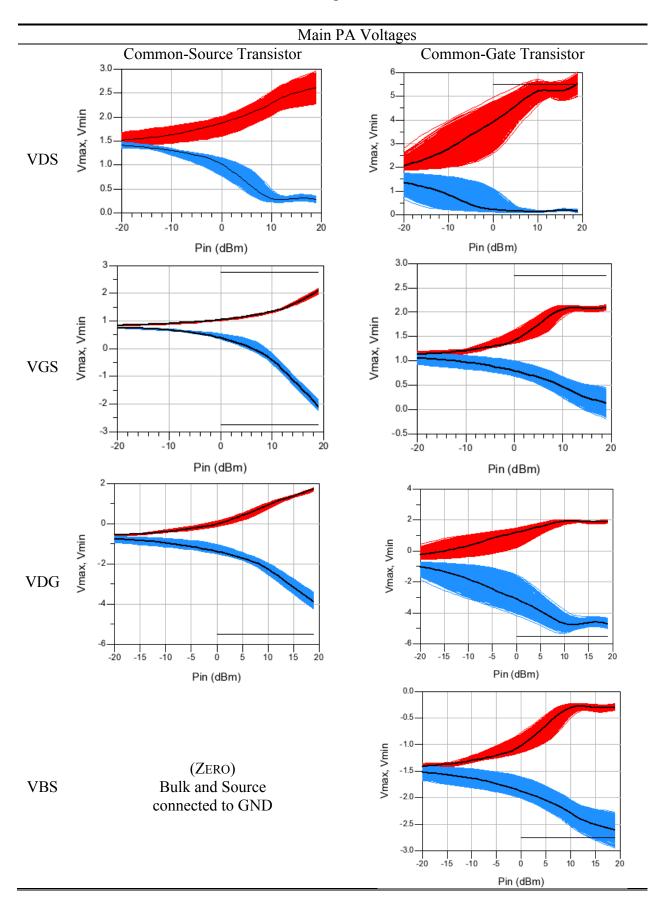

| voltages and Monte Carlo simulations                                            |             |

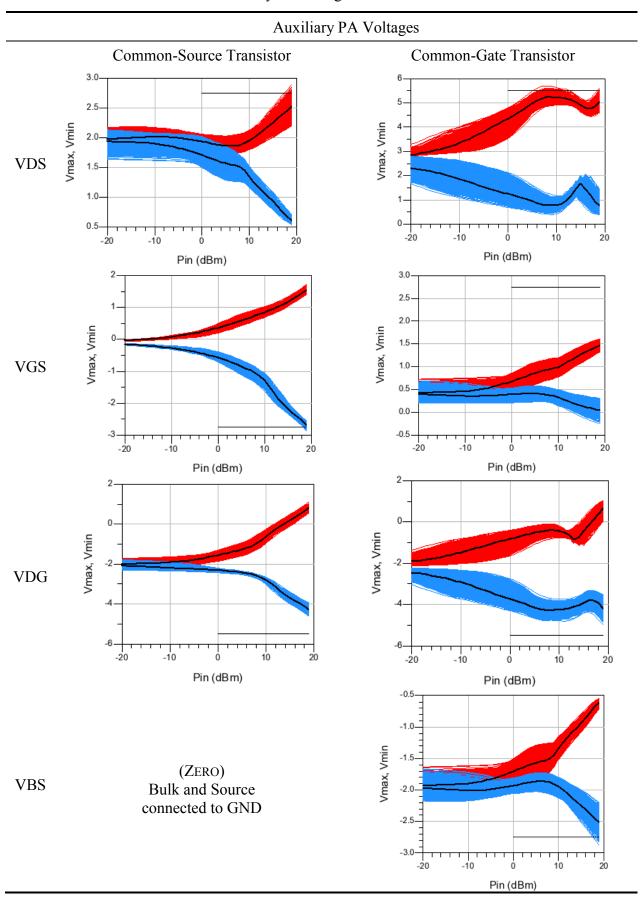

| Table 4.11 – Auxiliary PA voltages and Monte Carlo simulations                  | 94          |

| Table 4.12 – Resistors                                                          |             |

| Table 4.13 – Capacitors                                                         |             |

| Table 4.14 – Inductors                                                          |             |

| Table 4.15 – Transistors**                                                      |             |

| Table 4.16 - Polarization                                                 | 103 |

|---------------------------------------------------------------------------|-----|

| Table 4.17 – Number of variables by component type                        | 104 |

| Table 4.18 – Number of variables by circuit type                          | 104 |

| Table 4.19 – Total number of variables in each circuit                    | 105 |

| Table 5.1 – Comparing currents from measures and simulations              | 112 |

| Table 5.2 – Comparing currents and voltages from measures and simulations | 112 |

| Table 5.3 – Project and chip parameters summary                           | 121 |

| Table 5.4 – Comparisons with the state-of-art                             | 122 |

## FIGURES LIST

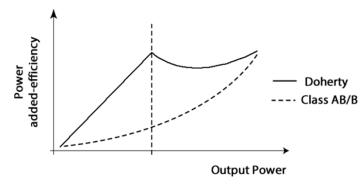

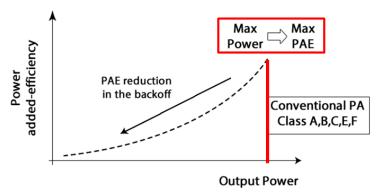

| Figure 1.1 - Comparing Doherty and Class AB/B power amplifier PAE performance sh                                                                               | 1ape6    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

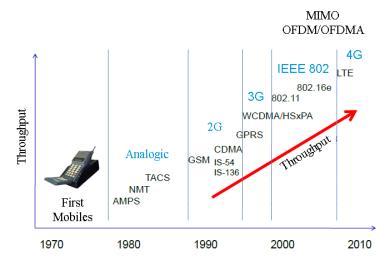

| Figure 2.1 – Wireless communication system evolution                                                                                                           | 10       |

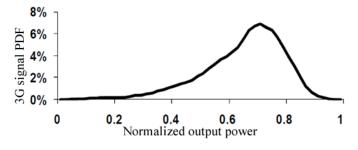

| Figure 2.2 – 3G signal PDF (UMTS - WCDMA) [10]                                                                                                                 | 10       |

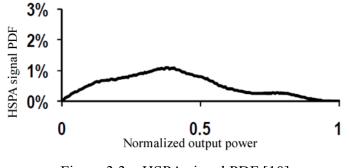

| Figure 2.3 – HSPA signal PDF [10]                                                                                                                              | 11       |

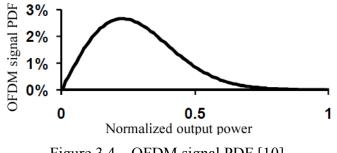

| Figure 2.4 – OFDM signal PDF [10]                                                                                                                              | 11       |

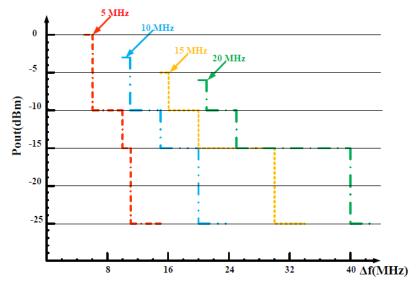

| Figure 2.5 – LTE power spectral mask [8]                                                                                                                       | 12       |

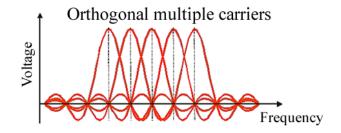

| Figure 2.6 – Multiple orthogonal carriers in OFDM.                                                                                                             | 14       |

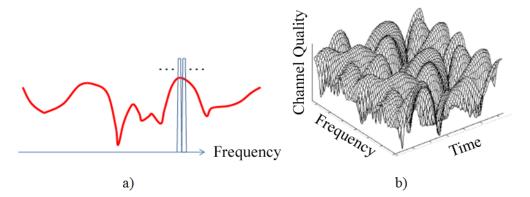

| Figure $2.7 - a$ ) Frequency variant channel seen as flat channel by the OFDM. b) Example 5.7 - a) Frequency variant channel seen as flat channel by the OFDM. | mple of  |

| frequency and time variant channel                                                                                                                             | 14       |

| Figure 2.8 – The SC/FDE and the OFDM [28].                                                                                                                     | 15       |

| Figure 2.9 – Block diagram of the SC-FDMA system                                                                                                               | 16       |

| Figure 2.10– iPhone 3 printed circuit board [30].                                                                                                              | 17       |

| Figure 3.1 – Simplified circuit with a power amplifier [35].                                                                                                   | 18       |

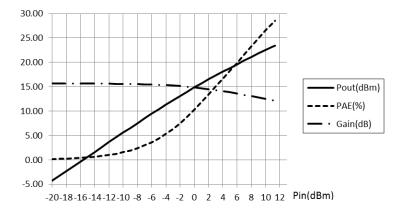

| Figure 3.2 – Main performance parameters in a PA                                                                                                               | 20       |

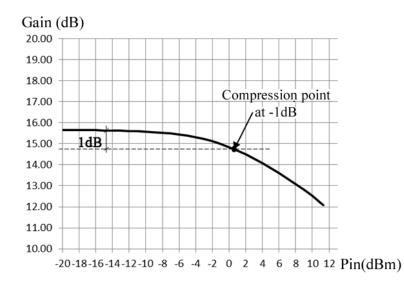

| Figure 3.3 – Compression point at -1dB seen by the gain performance.                                                                                           | 21       |

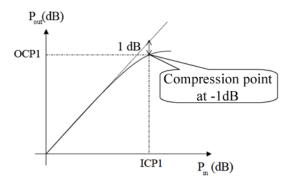

| Figure 3.4 – Compression point at -1dB [35]                                                                                                                    | 21       |

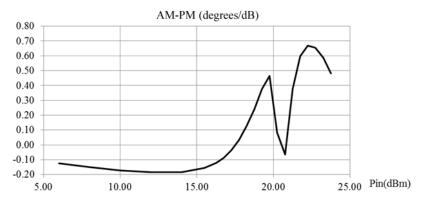

| Figure 3.5 – Phase distortion or AM/PM distortion                                                                                                              | 22       |

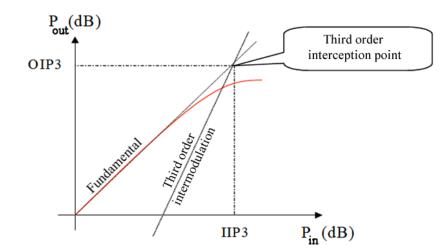

| Figure 3.6 – Third order interception point [35].                                                                                                              | 22       |

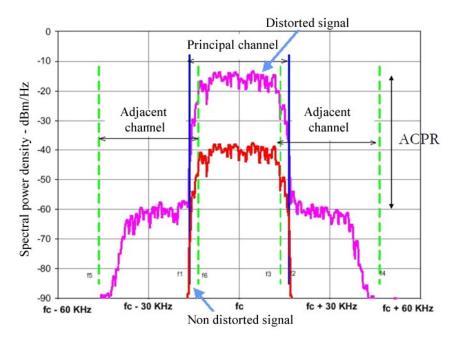

| Figure 3.7 – Distorted modulated signal spectrum provided by a non-linear PA [35]                                                                              | 23       |

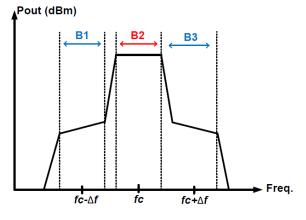

| Figure 3.8 – ACLR mask                                                                                                                                         | 23       |

| Figure 3.9 – PAE performance curve from conventional                                                                                                           | 24       |

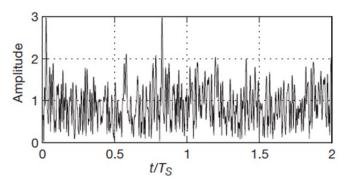

| Figure 3.10 – OFDM signal in time domain.                                                                                                                      | 24       |

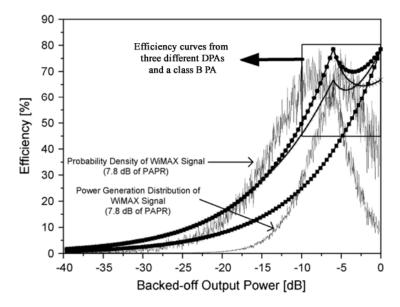

| Figure 3.11 – Ideal efficiencies for class B and Doherty PAs and the PDF of a WiMAX                                                                            | K signal |

| with 7.8dB PAPR [40]                                                                                                                                           | 25       |

| Figure 3.12 – Common source topology                                                                                                                           | 26       |

| Figure 3.13 – Cascode topology                                                                                                                                 | 27       |

| Figure 3.14 – Differential topology                                                                                                                            |          |

| Figure 3.15 – Differential cascode topology                                                                                                                    |          |

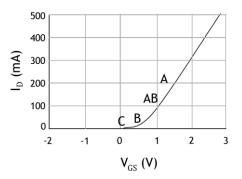

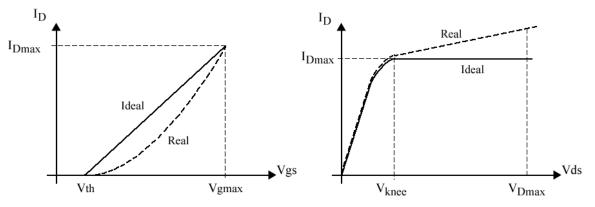

| Figure 3.16 – Drain current Id versus gate voltage Vgs                                                                                                         | 29       |

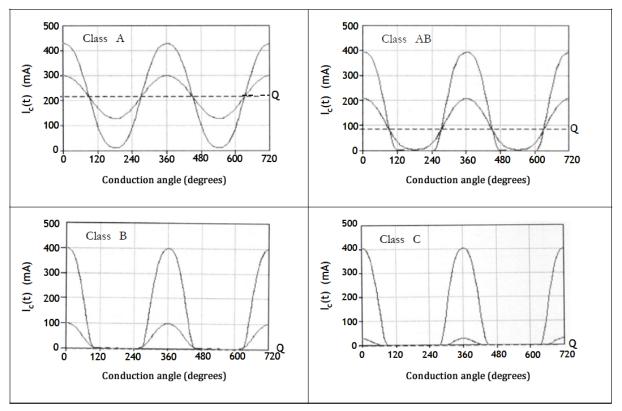

| Figure 3.17 – Summary of PAs classes A, AB, B and C [35]                                                                                                       | 29       |

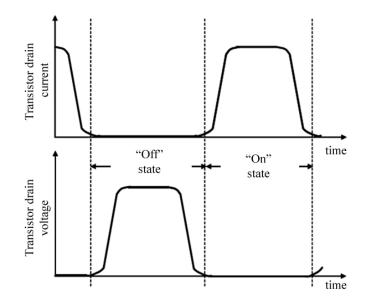

| Figure 3.18 – Transistor current and voltage waves in time domain [35]                                                                                         |          |

| Figure 3.19 – Class E basic topology                                                                                                                           |          |

| Figure 3.20 – Class F PA topology.                                                    |          |

|---------------------------------------------------------------------------------------|----------|

| Figure 3.21 – Class F PA signal wave shapes.                                          |          |

| Figure 3.22 - Examples of PAE and output power curves from the load-pull/sou          | rce-pull |

| methods                                                                               |          |

| Figure 3.23 – Methodology for determining optimal input and output PA impedances.     |          |

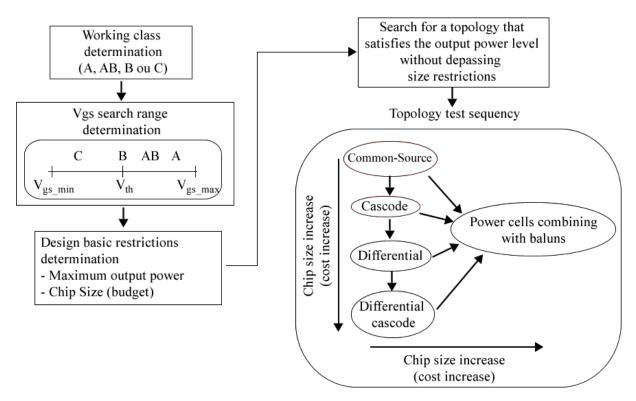

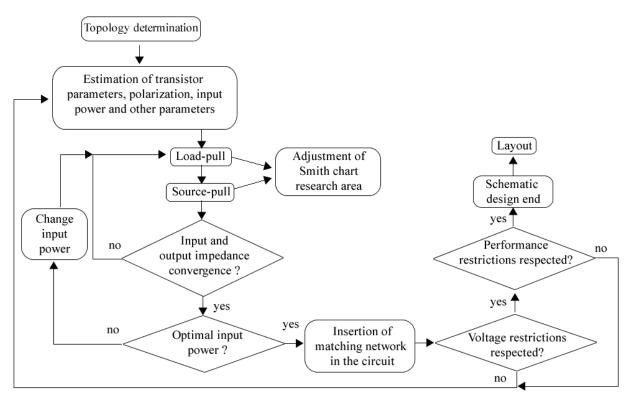

| Figure 3.24 – Flowchart for defining PA polarization and topology.                    |          |

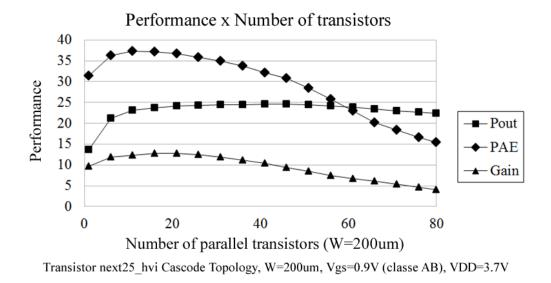

| Figure 3.25 - Cascode PA Class AB performance study for the number of transi          | stors in |

| parallel.                                                                             |          |

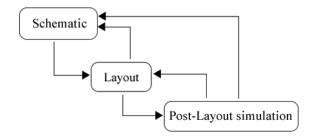

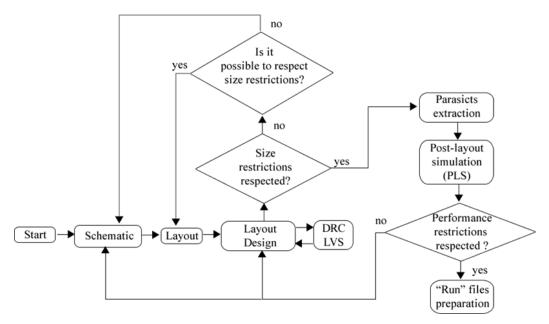

| Figure 3.26 – Simplified design cycle for integrated PAs                              |          |

| Figure 3.27 – Design cycle of the schematic                                           |          |

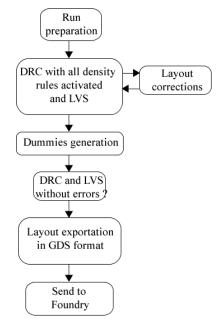

| Figure 3.28 – Layout design flowchart                                                 |          |

| Figure 3.29 – Final process on the chip design                                        |          |

| Figure 3.30 - Parameters to control the PA efficiency; a) polarization current, b)    | voltage  |

| supply VDD, c) load impedance                                                         | 40       |

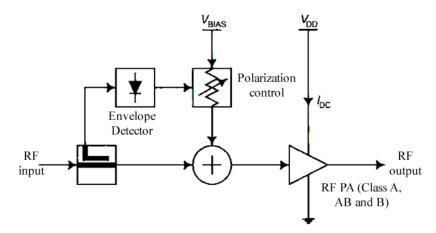

| Figure 3.31 – Dynamic polarization technique diagram [37]                             | 41       |

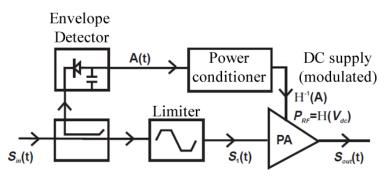

| Figure 3.32 – Envelope elimination and restoration system [1]                         | 41       |

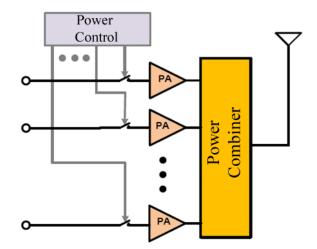

| Figure 3.33 – Power cell switching techniques diagram [44].                           |          |

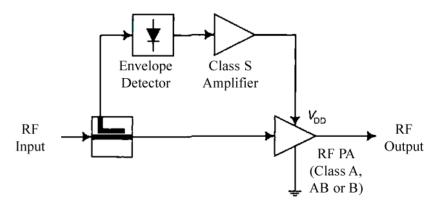

| Figure 3.34 – Schematic of a RF PA using the ET technique [37].                       |          |

| Figure 3.35 - Bypass stage technique structure                                        | 43       |

| Figure 3.36 – Bypass stage technique and its operation modes [49]                     | 44       |

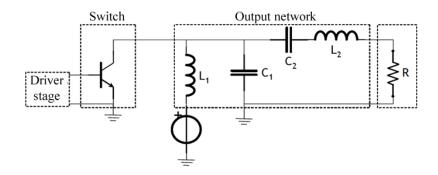

| Figure 3.37 – Doherty power amplifier simplified schematic                            | 44       |

| Figure 3.38 – Doherty power amplifier theoretical drain efficiency [1]                | 45       |

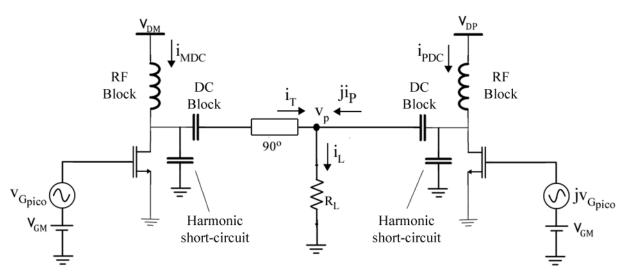

| Figure 3.39 – Simplified scheme of Doherty power amplifier                            | 46       |

| Figure 3.40– Transistors as voltage controlled current sources                        | 47       |

| Figure 3.41 – Transmission line voltages and currents                                 | 47       |

| Figure 3.42 - Relations between the auxiliary transistors drain parameters and the vo | ltage on |

| the gate of the main transistor.                                                      |          |

| Figure 3.43 - Drain efficiency of the Doherty power amplifier and drain impedance     | e of the |

| main PA                                                                               |          |

| Figure 3.44 – Sub-PAs currents behavior                                               |          |

| Figure 3.45 – Doherty power amplifier ideal circuit [50]                              |          |

| Figure 3.46 – Real and ideal transistor's model                                       | 50       |

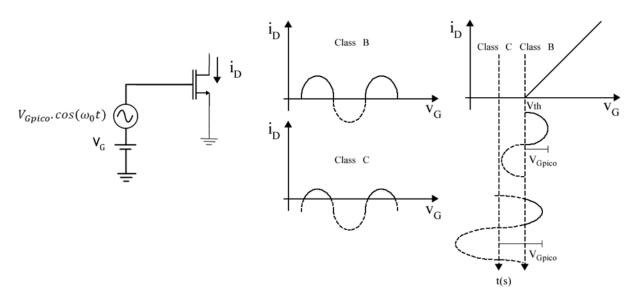

| Figure 3.47 – Transistor gate voltage and sub-PA classes                              | 51       |

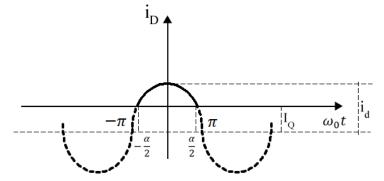

| Figure 3.48 – Transistor conduction angle                                             |          |

| Figure 3.49 - Relation between the constant efficiency and the sub-PAs currents behavior   | .55  |

|--------------------------------------------------------------------------------------------|------|

| Figure 3.50 – Impact of the Vknee voltage on the DPA efficiency                            | .56  |

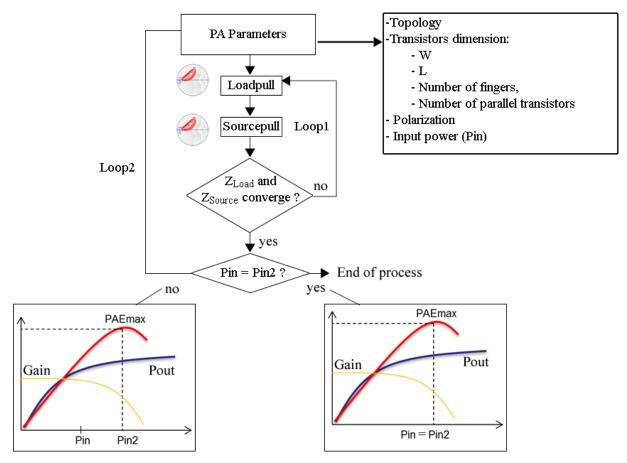

| Figure 4.1 – Cascode PA design flowchart                                                   | .62  |

| Figure 4.2 – Simplified diagram of the design cycle of the Doherty Power Amplifier         | .65  |

| Figure 4.3 – Doherty Power Amplifier impedance analysis                                    | .66  |

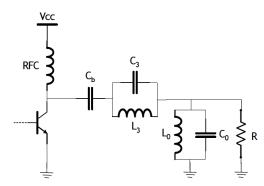

| Figure 4.4 – Topology of the cascode sub-PA                                                | .68  |

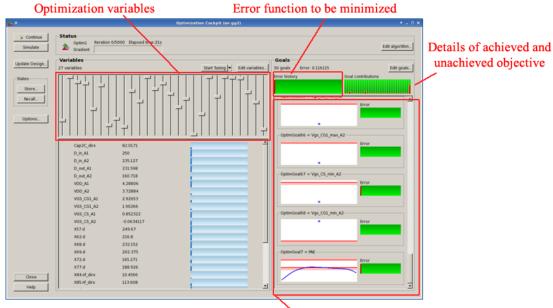

| Figure 4.5 – Diagram of the sub PA design optimization schematic.                          | .70  |

| Figure 4.6 – Next25_hvi transistor with its six pins                                       | .71  |

| Figure 4.7 – Next25_hvi transistor layout                                                  | .71  |

| Figure 4.8 – Voltage analysis stages. Voltages in frequency domain (a), voltages on the ti | ime  |

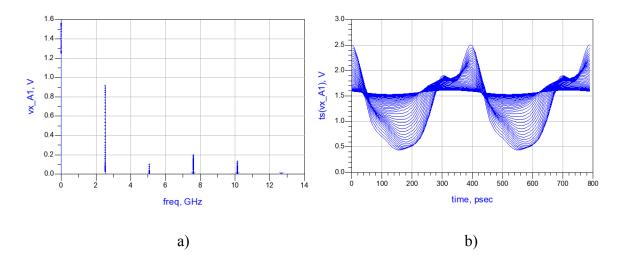

| domain (b), maximum and minimum voltages versus the input power (c)                        | .73  |

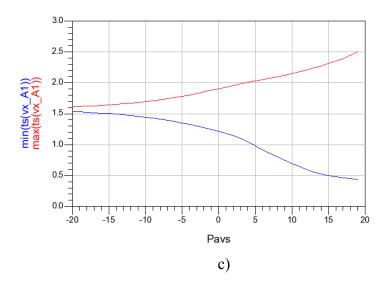

| Figure 4.9 – ADS optimization cockpit                                                      | .74  |

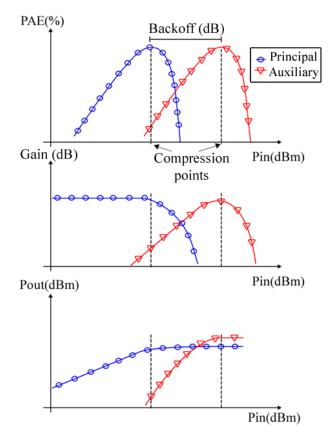

| Figure 4.10 – Main and auxiliary PA performance curves of PAE, gain and output power       | .76  |

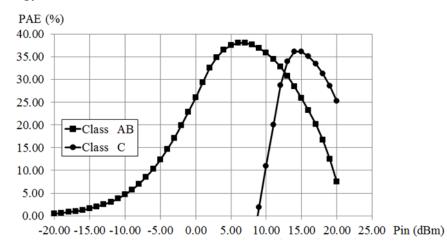

| Figure 4.11 – Sub-PAs PAE performance before being connected as DPA                        | .76  |

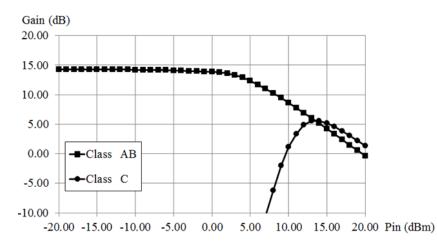

| Figure 4.12 – Sub-PAs gain performance before being connected as DPA                       | .77  |

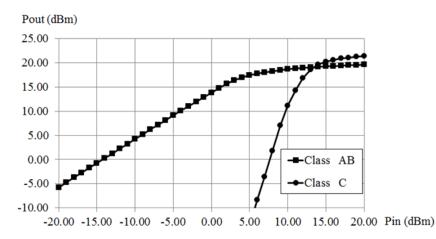

| Figure 4.13 – Sub-PAs output power performance before being connected as DPA               | .77  |

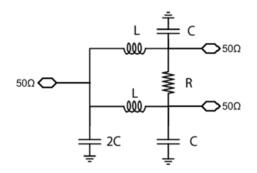

| Figure 4.14 – Wilkinson power splitter schematic                                           | .79  |

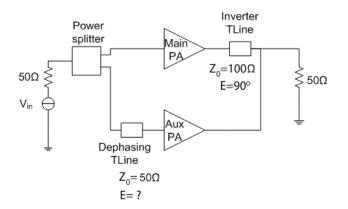

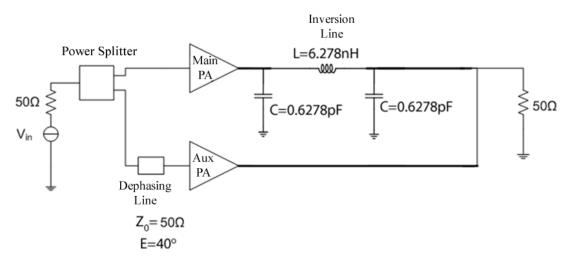

| Figure 4.15 – Doherty Power Amplifier simplified schematic                                 | .80  |

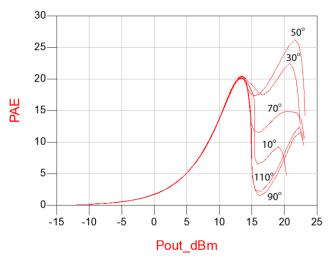

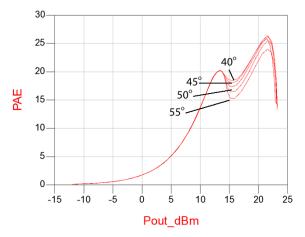

| Figure 4.16 - PAE x Pout performance for a sweep simulation on the electric length of      | the  |

| dephasing transmission line                                                                | .80  |

| Figure 4.17 – Tuning the transmission line electrical length value                         | .81  |

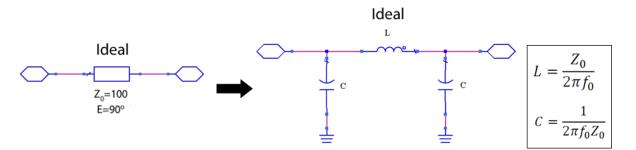

| Figure 4.18 – Lumped <sup>1</sup> / <sub>4</sub> wave transmission line PI model           | . 82 |

| Figure 4.19 – Inverting transmission line replaced by PI model                             | . 82 |

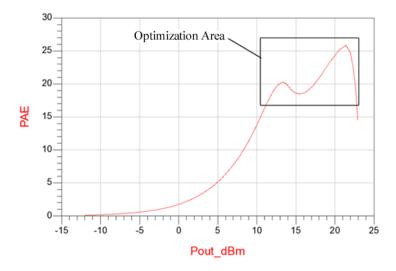

| Figure 4.20 – Optimization region                                                          | . 82 |

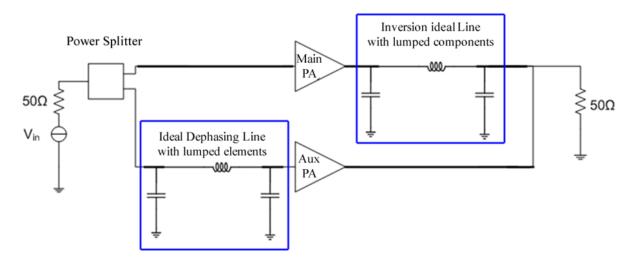

| Figure 4.21 – Simplified schematic with lumped ideal transmission lines                    | .83  |

| Figure 4.22 - Components replacing sequence. a) First stage. b) Replacing the inductor     | : c) |

| Replacing capacitors                                                                       | .83  |

| Figure 4.23 – Detailed topology of the DPA with only fabricant components                  | .85  |

| Figure 4.24 – Performance of the Doherty Power Amplifier                                   | .85  |

| Figure 4.25 – Chip area estimation                                                         | .86  |

| Figure 4.26 – Input and output network matching optimization                               | .87  |

| Figure 4.27 – Final topology of the circuit                                                | .87  |

| Figure 4.28 – Increase on PAE performance due to changes on the input and output netwo     | orks |

|                                                                                            | .88  |

| Figure 4.29 - Increase on Gain performance due to changes on the input and output networks     |

|------------------------------------------------------------------------------------------------|

|                                                                                                |

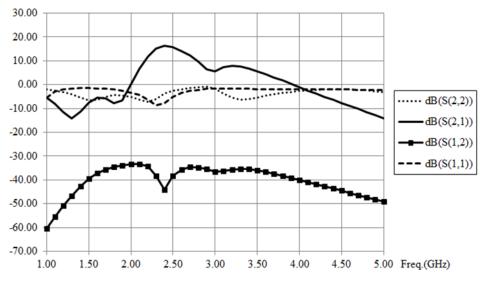

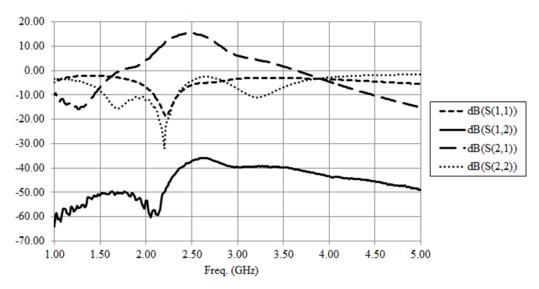

| Figure 4.30 – S-parameter simulation of the DPA schematic                                      |

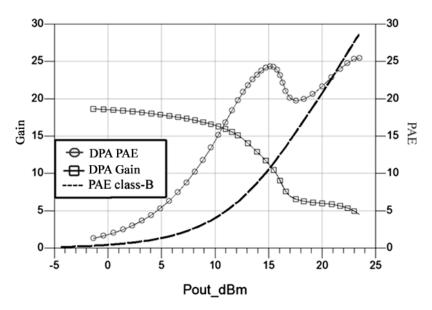

| Figure 4.31 – PAE and gain performance of the DPA schematic and the PAE performance of         |

| a class B PA schematic                                                                         |

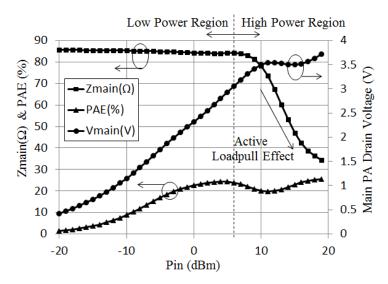

| Figure 4.32 – Load modulation (Zmain) and constant voltage (Vmain) on the main PA drain        |

|                                                                                                |

| versus the input power) and DPA PAE                                                            |

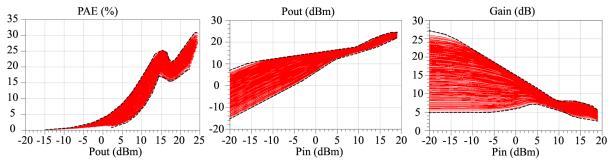

| Figure 4.34 – Monte Carlo simulations for performance variationTable 4.10 – Main PA            |

| voltages and Monte Carlo simulations92                                                         |

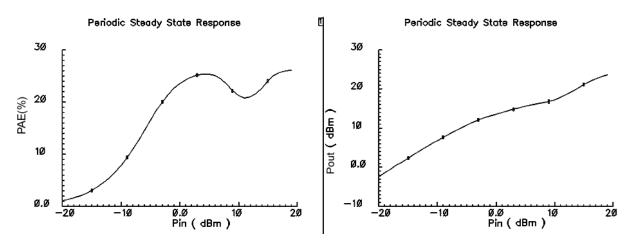

| Figure 4.35 – PAE and Pout performance versus input power in CADENCE                           |

| Figure 4.36 – Gain performance versus input power in CADENCE                                   |

| Figure 4.37 – Doherty Power Amplifier layout sent for fabrication                              |

| Figure 4.38 – Post-layout S-parameters simulation                                              |

| Figure 4.39 – Post-layout large signal performance simulation                                  |

| Figure 4.40 – Signal path highlighted                                                          |

| Figure 4.41 – Position and organization of adjacent transistors in layout                      |

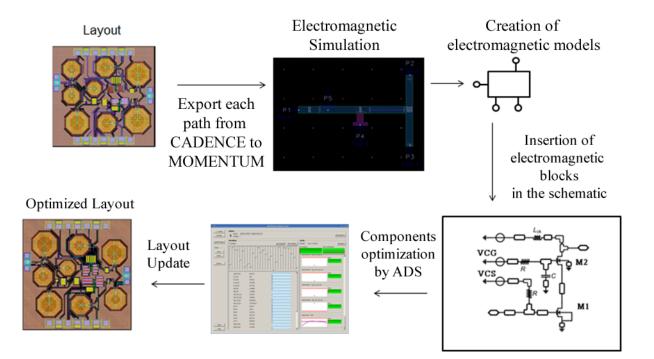

| Figure 4.42 – Process of electromagnetic paths modeling and circuit re-optimization 100        |

| Figure 4.43 – a) Layout before electromagnetic optimization. b) Layout after electromagnetic   |

| optimization101                                                                                |

| Figure 4.44 - Simulations comparing the PAE between post-layout, schematic and schematic       |

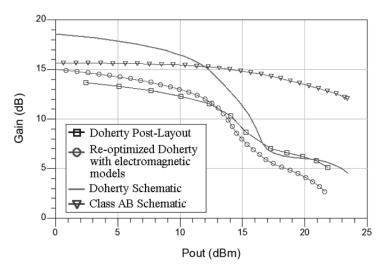

| with electromagnetic models from DPA and schematic from a class B PA101                        |

| Figure 4.45 - Simulations comparing the gain between post-layout, schematic and schematic      |

| with electromagnetic models from DPA and schematic from a class B PA102                        |

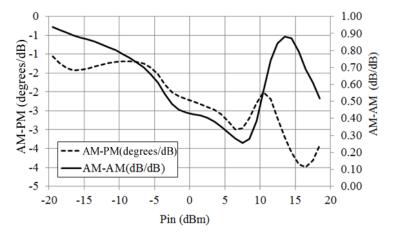

| Figure 4.46 – AM-AM and AM-PM distortion curves105                                             |

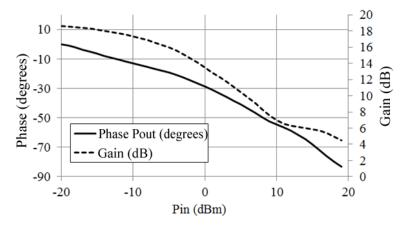

| Figure 4.47 – Input data for the LTE signal simulation: gain and output signal phase106        |

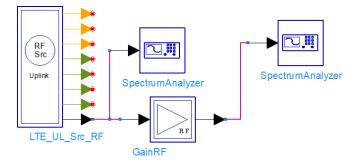

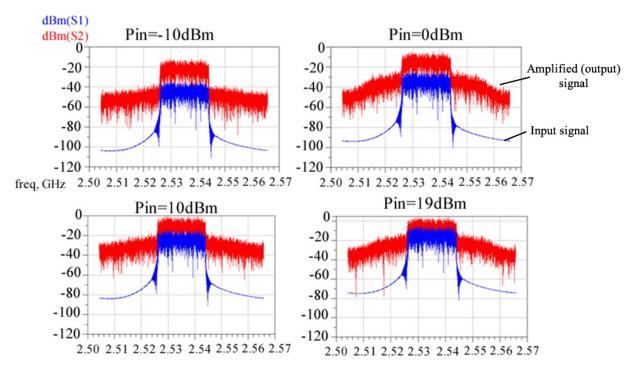

| Figure 4.48 – Schematic simulation of the LTE signal in ADS                                    |

| Figure 4.49 - Power spectral density of the input signal (blue) and output signal (red) of the |

| DPA for different input power                                                                  |

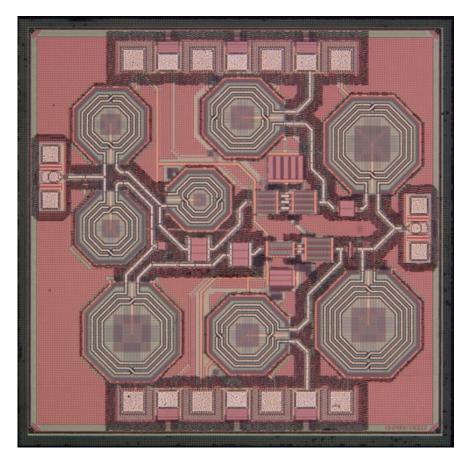

| Figure 5.1 – Chip photograph                                                                   |

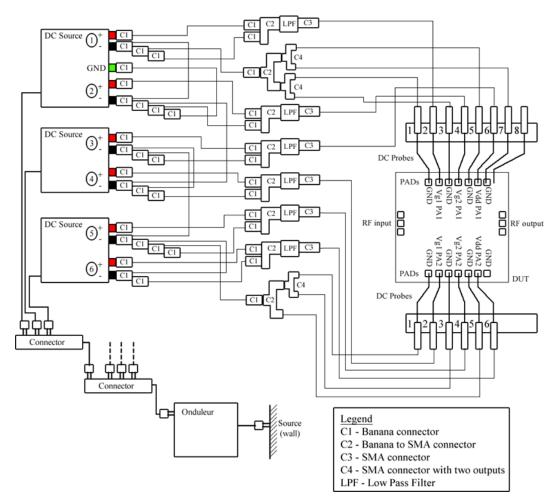

| Figure 5.2 – DC polarization setup                                                             |

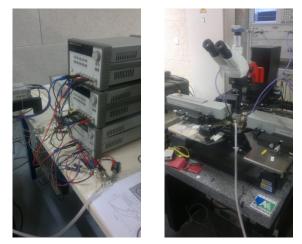

| Figure 5.3 – DC sources, cables, connectors (left), microscope and RF pointers (right)110      |

| Figure 5.4 – RF setup                                                                          |

| Figure 5.5 – Details of RF and DC polarization setup                                         | 11 |

|----------------------------------------------------------------------------------------------|----|

| Figure 5.6 – S-parameters measures with the circuit biased with nominal voltages1            | 13 |

| Figure 5.7 – PAE and Gain measures with nominal voltages in 2.5 GHz                          | 13 |

| Figure 5.8 – S-parameters measures with the circuit biased with optimal voltages1            | 14 |

| Figure 5.9 - PAE measures with the DPA biased with optimal voltages in 2.4, 2.5 at           | nd |

| 2.6GHz and the PAE simulated performance of a class B PA schematic1                          | 14 |

| Figure 5.10 – Gain measures for the DPA with optimal voltages in 2.4, 2.5 and 2.6GHz at      | nd |

| simulated gain performance of a class B PA schematic1                                        | 15 |

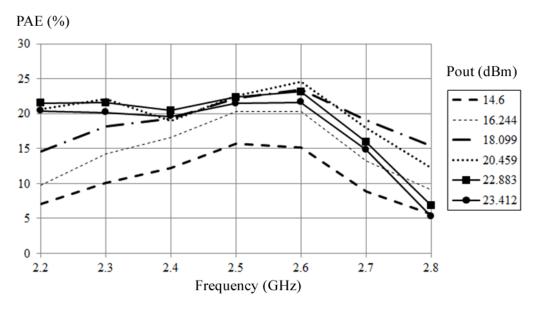

| Figure 5.11 – Frequency band measures with DPA biased with optimal voltages1                 | 15 |

| Figure 5.12 - PAE measures with optimal voltages for frequencies between 2.2 GHz at          | nd |

| 2.8 GHz1                                                                                     | 16 |

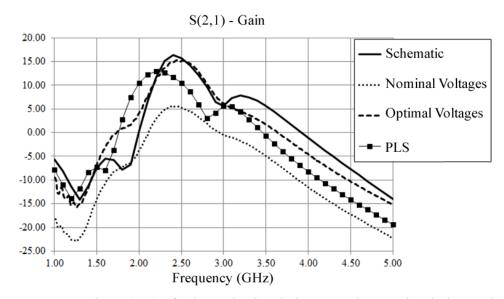

| Figure 5.13 – Comparing S(2,1) of schematic simulation, post-layout simulation and measur    | es |

| with nominal and optimal voltages1                                                           | 17 |

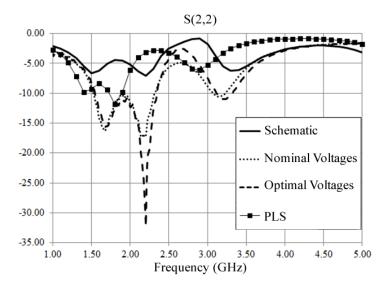

| Figure 5.14 – Comparing S(2,2) of schematic simulation, post-layout simulation and measur    | es |

| with nominal and optimal voltages1                                                           | 18 |

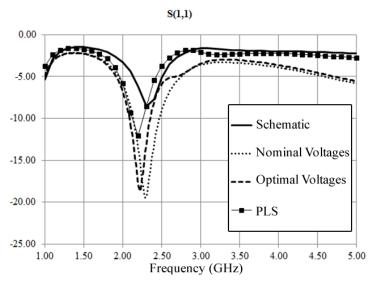

| Figure 5.15 - Comparing S(1,1) of schematic simulation, post-layout simulation and measur    | es |

| with nominal and optimal voltages1                                                           | 18 |

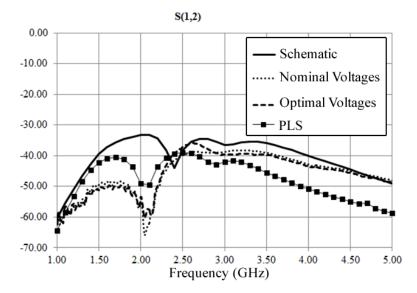

| Figure 5.16 - Comparing $S(1,2)$ of schematic simulation, post-layout simulation and measure | es |

| with nominal and optimal voltages1                                                           | 19 |

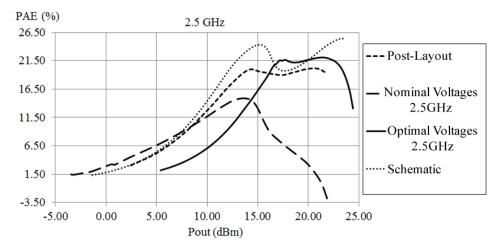

| Figure 5.17 – PAE performance of schematic, post-layout and measures in 2.5GHz1              | 19 |

| Figure 5.18 - PAE performance of schematic, post-layout and nominal measures in 2.5 GH       | Ηz |

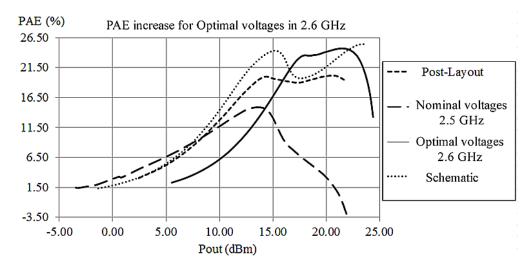

| and optimal measures in 2.6 GHz12                                                            | 20 |

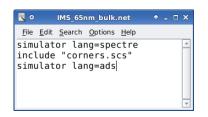

| Figure A.6.1 –NETLIST INCLUDE component proprieties details                                  | 34 |

| Figure A.6.2– IMS_65nm_bulk.net file                                                         | 35 |

| Figure A.6.3 – Corners.scs file details                                                      | 36 |

| Figure A.6.4 – Component pins details                                                        | 38 |

| Figure A.6.5 – Detail of the window of component parameters insertion                        | 38 |

| Figure A.6.6 – Component symbol creation                                                     | 39 |

# LIST OF SYMBOLS, NOMENCLATURES AND ABBREVIATIONS

| 3G/4G   | - | Third/Fourth generation                            |

|---------|---|----------------------------------------------------|

| 3GPP    | - | 3rd Generation Partnership Project                 |

| ACLR    | - | Adjacent channel leakage ratio                     |

| ACPR    | - | Adjacent-Channel Power Ratio                       |

| ADS     | - | Advanced Design System                             |

| BTS     | - | Base station                                       |

| CDMA    | - | Code Division Multiple Access                      |

| CG      | - | Common Gate                                        |

| СР      | - | Cyclic prefix                                      |

| CS      | - | Common Source                                      |

| DFT     | - | Discrete Fourier Transform                         |

| DK      | - | Design Kit                                         |

| DPA     | - | Doherty Power Amplifier                            |

| EER     | - | Envelope elimination and restoration               |

| ET      | - | Envelope Tracking                                  |

| FDMA    | - | Frequency Division Multiple Access                 |

| IDFT    | - | Inverse Discrete Fourier Transform                 |

| IMD     | - | Inter modulation distortion                        |

| LTE     | - | Long Term Evolution                                |

| MIMO    | - | Multiple input multiple output                     |

| OFDM    | - | Orthogonal Frequency Division Multiplexing         |

| OFDMA   | - | Orthogonal Frequency Division Multiplexing Access  |

| PA      | - | Power Amplifier                                    |

| PAE     | - | Power added efficiency                             |

| PAPR    | - | Peak-to-Average Ratio                              |

| PBO     | - | Power backoff                                      |

| PCB     | - | Printed circuit board                              |

| PLS     | - | Post-Layout simulation                             |

| RF      | - | Radio frequency                                    |

| SC/FDE  | - | Single carrier with frequency domains equalization |

| SC-FDMA | - | Single Carrier Frequency Division Multiple Access  |

| SoC     | - | System on Chip                                     |

|         |   |                                                    |

- TDMA Time Division Multiple Access

- WiMAX Worldwide Interoperability for Microwave Access

- WWAN Wireless Wide Area Network

#### **2** INTRODUCTION

#### 2.1 MOTIVATION

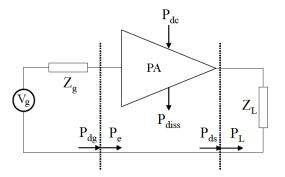

The telecommunication market observes nowadays a growing demand for radio frequency (RF) mobile devices. One of the major requirements of these systems is the high efficiency on energy use in order to extend the battery life in mobile devices. Among the main RF transmission subsystems, power amplifiers (PA) found in transmitters have been recognized as one of the RF chain blocks that dissipates most energy [1].

Conventional PAs class A, B, AB and C present maximum efficiency only at maximum output power level. As long as the signal power decreases, the amplifier efficiency also decreases and very quickly. The new communication standards LTE/LTE-Advanced (4G standard) [2] presents amplitude modulation which makes conventional PAs to work with an average efficiency much less than its maximum.

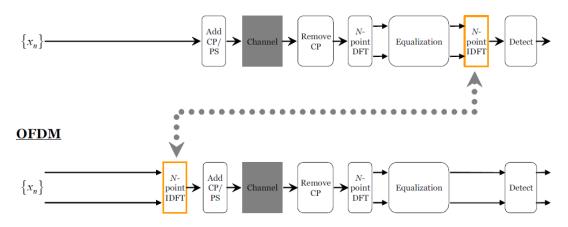

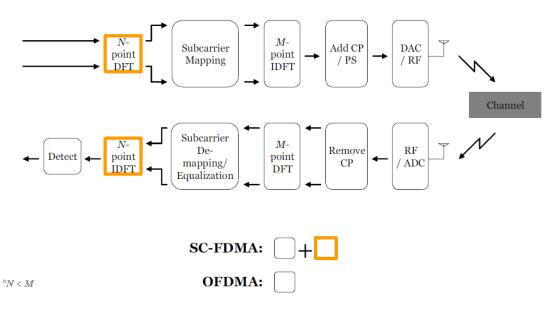

Another characteristic of these new communication standards is the high peak-to-average power ratio (PAPR). Communication systems evolution have been heading towards the use of several sub-carriers in transmission using orthogonal frequency division multiplexing (OFDM) due to its robustness in channels that presents high variations, frequency selectivity and multipath. The high PAPR characteristic makes the signal to stay in low and medium power levels most of the time, where conventional PAs have a very low efficiency. In theory, an OFDM signal with 52 sub-carriers has a 17dB PAPR [3]. The use of communication standards with high PAPR in a conventional PA makes it to work with a low efficiency level, which decreases the battery life and produce high energy dissipation (heating) [4] [1] [5].

For these reasons, the 4G standard has chosen the single carrier frequency division multiple access (SC-FDMA) at the uplink [6], with maximum output power of 23dBm [7], QPSK and 16-QAM modulation [8], presenting a maximum PAPR of 7.03dB on the 16-QAM [9]. Therefore, all effort towards increasing the efficiency on the transmission of high PAPR signals, increasing PA efficiency at low and medium output power levels is of great interest to the mobile telecommunication industry.

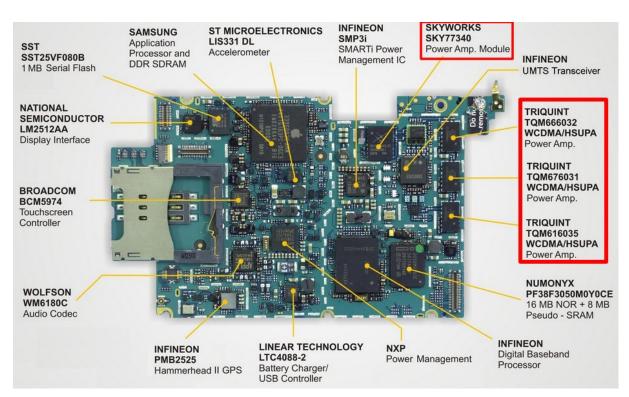

Beyond the demand on increasing the battery time of use, the market has been demanding the increase of functions inserted into these devices and its price reduction. This demand indicates the integration trend of multiple circuits, both digital and analog, inside the same chip (system-on-chip, SoC) and the use of low cost silicon based technologies.

#### 2.2 PROPOSED SOLUTION

In order to design a PA more suitable for high PAPR signals (3G/4G), Table 2.1, and to comply the integration and low cost trend, this work proposes the design of an optimized Doherty Power Amplifier (DPA) with all its components integrated in Complementary Metal-Oxide Semiconductor (CMOS) 65nm technology from STMicroelectronics.

| Standard                      | PAPR        |

|-------------------------------|-------------|

| 3G UMTS - WCDMA [10]          | 3dB         |

| UMTS 3G extension - HSPA [10] | 4.9 - 7.2dB |

| 4G LTE uplink – SC-FDMA [10]  | 7.03dB      |

Table 2.1 – PAPR for 3G/4G Standards

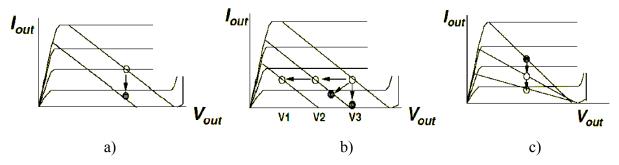

The DPAs represent an efficiency enhancement technique [1] for PAs used to maintain the efficiency (transistor's drain efficiency and power added-efficiency – PAE) at a constant level inside a range of output power values, starting from the maximum output power level until low/medium levels, to cover all demanded levels by the signal standard (amplitude modulated signal). So, even with a high PAPR, the PA remains inside a same PAE level. Other advantage of the DPA is the fully analog control of the efficiency enhancement on the backoff. Efficiency enhancement with digital control reduces the bandwidth and increases circuit size and complexity. The DPA topology also does not exclude the application possibility of other techniques to increase the efficiency and/or linearity performance.

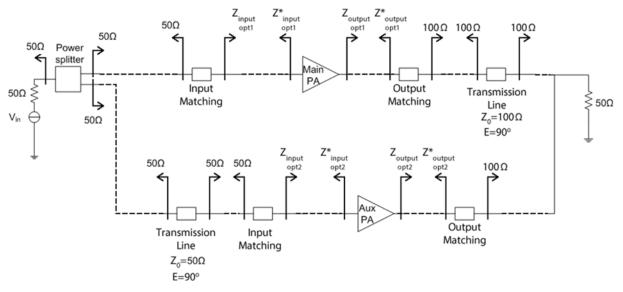

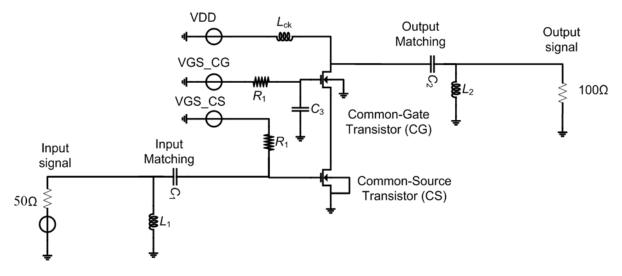

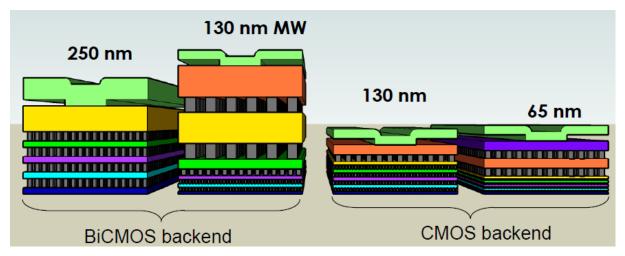

The 65nm CMOS technology of STMicroelectronics is better suited for digital circuits, due to its reduced thickness (12.9µm total thickness for 12 metal layer technology [11]), being therefore, a challenge for PAs implementation. The DPA is a technique widely used for radiobase stations [12] [13] [14], normally implemented in printed circuit boards (PCBs). Many works have already attempted to fully integrate a DPA into low cost technologies [3] [15] [16] [17], however the DPA essential characteristic of constant PAE has not been implemented with full integration in CMOS 65nm technology, allowing the PA integration with other circuits of the RF transmission chain on the same chip.

This work proposes the fully integration of a low cost DPA in CMOS 65nm technology of STMicroelectronics for mobile applications with high PAPR characteristic (3G/4G). Specifications are defined for the last mobile communication standard, the LTE, (official standard 3GPP TS 36.104 V8.4.0), shown in Table 2.2. The frequency chosen for the design is the 2.535GHz (LTE uplink standard central frequency for Europe, Asia and Brazil) and among the DPA main specifications (Table 2.3) there are the constant PAE performance with more than 8dB output power backoff range and with maximum output power of 23dBm (design simulation). The circuit measures presented a constant PAE inside a 7dB backoff range in a frequency band of 200MHz, starting at 2.4GHz up to 2.6GHz, and 23.5dBm output power.

| <b>LTE specifications</b><br>Source (Standard): 3GPP TS 36.104 V8.4.0 |                                   |  |  |  |

|-----------------------------------------------------------------------|-----------------------------------|--|--|--|

| Specification Value                                                   |                                   |  |  |  |

| Frequency                                                             | 2500MHz – 2570MHz                 |  |  |  |

| Modulation (uplink)                                                   | QPSK,16-QAM, 64-QAM               |  |  |  |

| PAPR                                                                  | 7.03dB [7]                        |  |  |  |

| Output power (uplink)                                                 | 23dBm [5]                         |  |  |  |

| Band                                                                  | 1.25 – 2.5 – 5 – 10 – 15 or 20MHz |  |  |  |

Table 2.2 – LTE specifications

The goal of this work is to develop a fully integrated DPA with a high backoff range according to the Doherty theory [1]. In the state of the art, it has not been showed in this technology [3] [15] [16] [17]. As a secondary objective, efforts were made in order to keep the low cost characteristic. The design of integrated circuits in CMOS technology allows the use of many metal layers in the chip, which can considerably raise the production cost. The 65nm CMOS technology allows using up to ten metal layers and MIM capacitors (high quality factor and small area). In order to avoid costs increase, only seven standard layers and MOM capacitors (fringe capacitors, low quality factor and large area) were used, which corresponds to 7.500 euros/mm<sup>2</sup> (price in the year 2012), Table 2.4. This price is for the

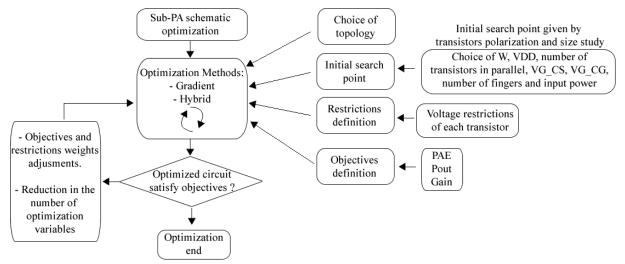

production of a prototype (25 samples of the chip are produced), for a large production the cost depends on several details and reduces drastically when divided by the number of chips. The DPA circuit was fully integrated: input and output network matching, transmission lines, choke inductances (RF block) and power splitter. The design methodology approach was based in optimization techniques [18] [19] employed on many stages of the design, specially the gradient and hybrid method, from the schematic of each sub-PA that composes the DPA, until its complete schematic, layout and re-optimization with electromagnetic models.

| Power amplifier topology | Doherty Power Amplifier                      |  |  |

|--------------------------|----------------------------------------------|--|--|

| Integration degree       | Fully integrated                             |  |  |

| Low cost characteristics | Silicon technology (65nm CMOS)               |  |  |

|                          | Only standard metal levels                   |  |  |

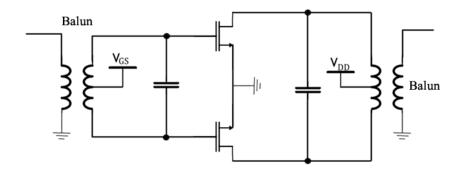

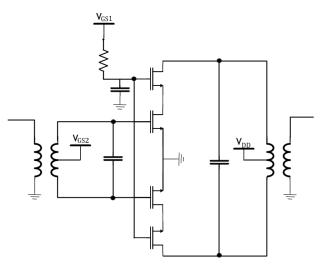

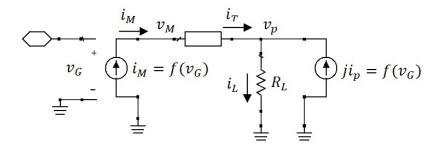

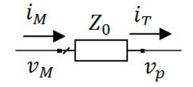

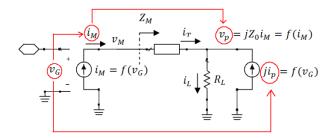

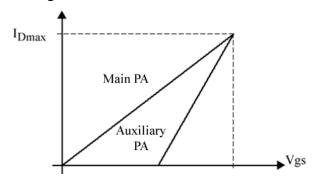

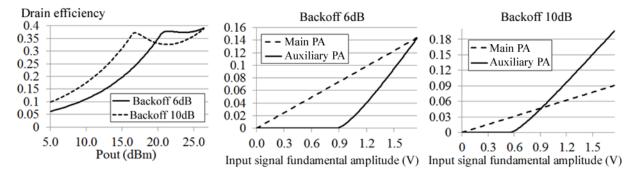

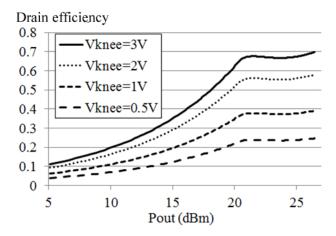

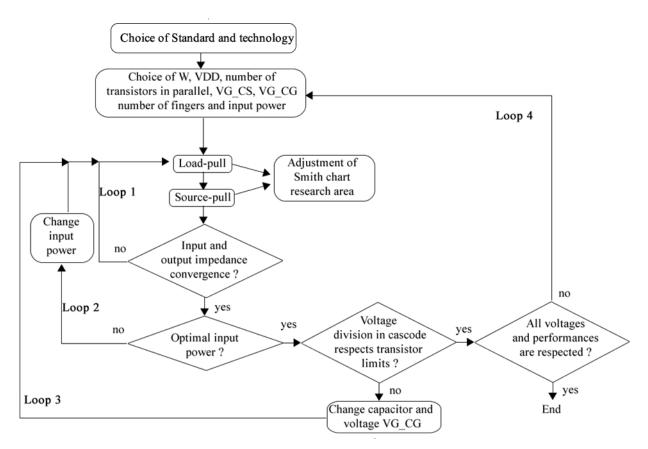

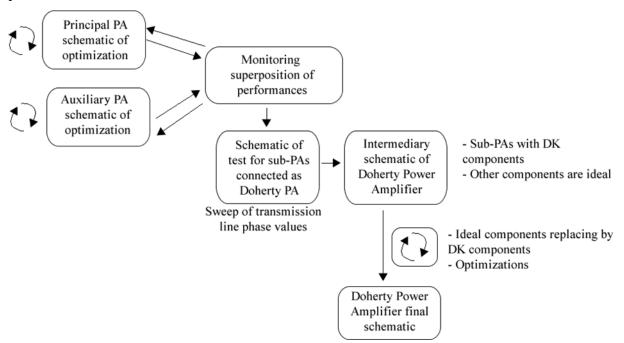

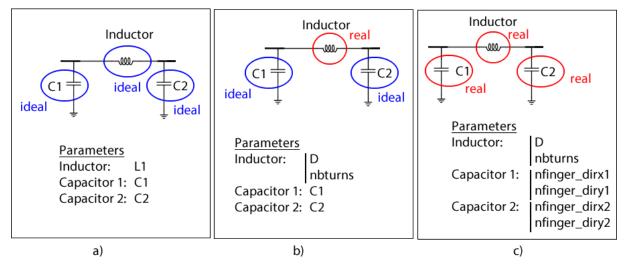

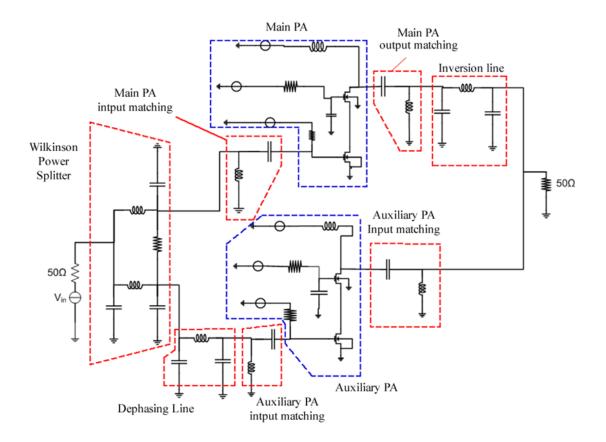

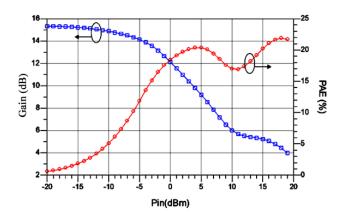

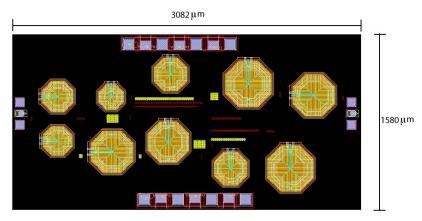

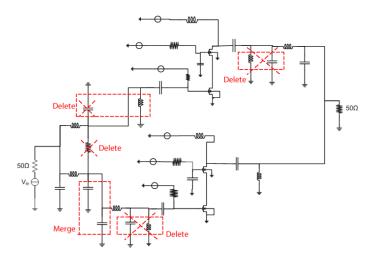

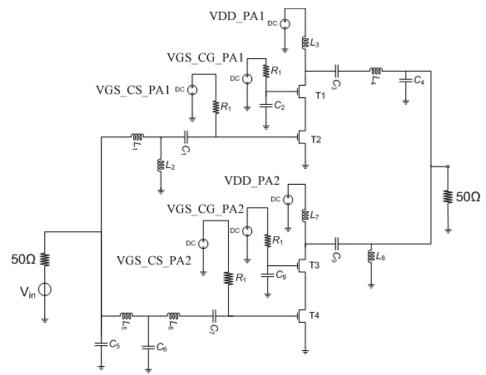

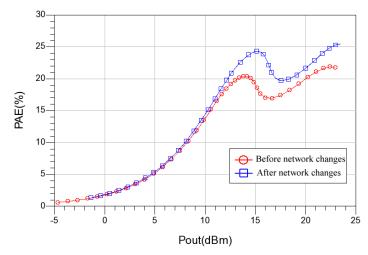

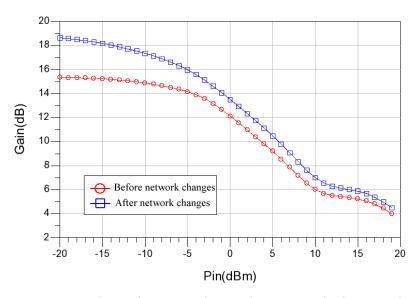

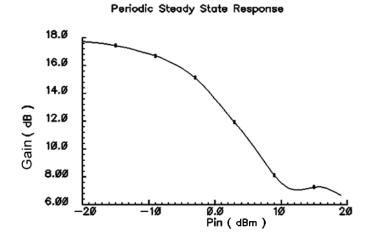

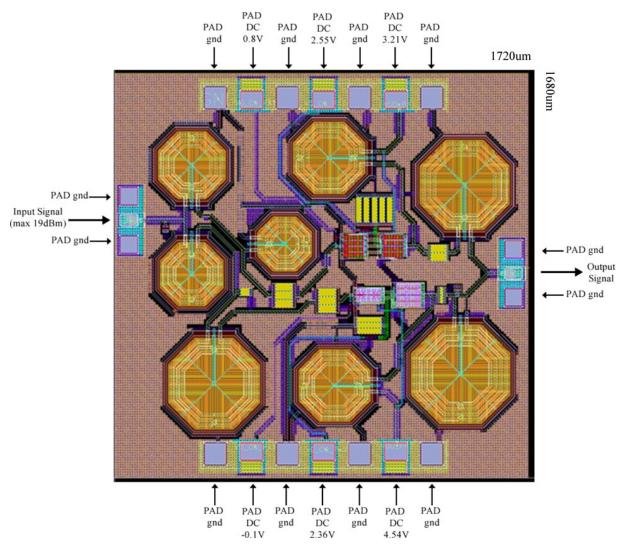

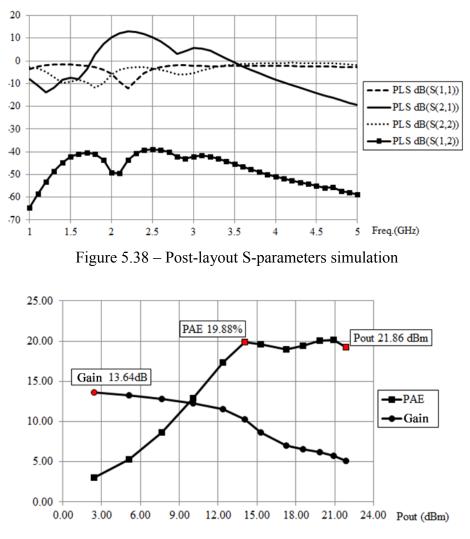

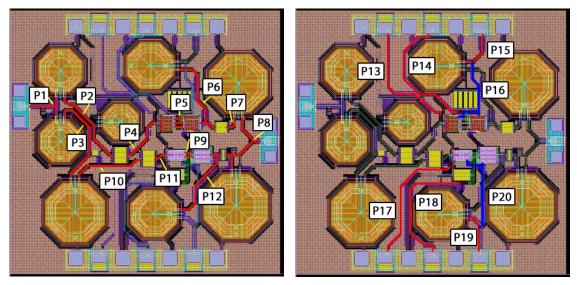

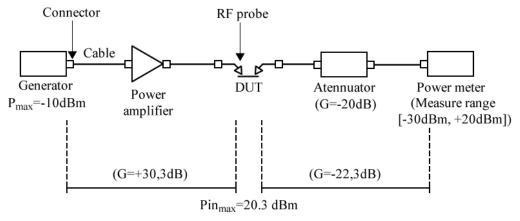

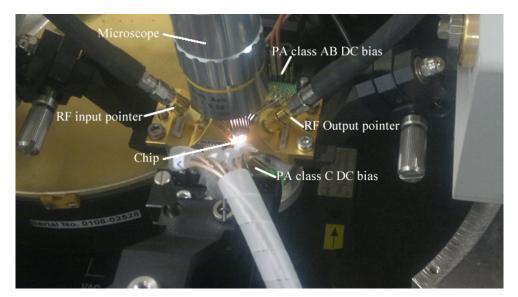

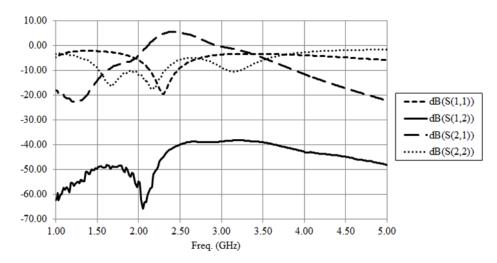

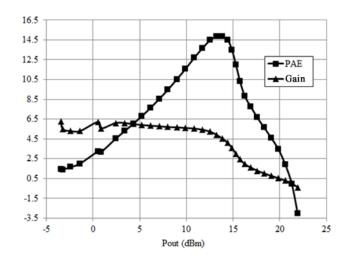

|                          | MOM capacitors                               |  |  |